前回のまとめに引き続き、今回よりインテルチップセットのロードマップを解説する。が、その前にまず「チップセットとはなんぞや」、という話を簡単に触れておく。

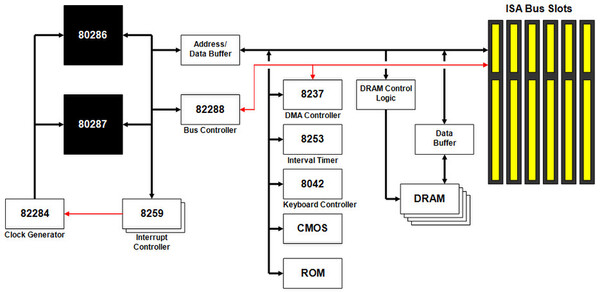

下の図1は、IBM PC/ATの内部構成をだいぶ簡略化したものである。この当時、PC/ATを構成するには7つのチップと、DRAMコントローラーやそのほかの周辺回路が必要であり、これらは独立したチップを使っていた。構成部品はかなり多かったわけだ。

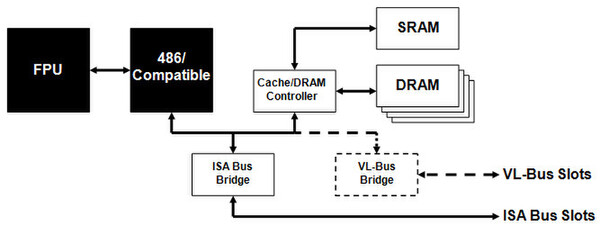

これがIntel486プロセッサーの時代になると、高性能化やデザインの容易さを考えて、だいぶ様相が変わった。図1では、メモリーを初めとする周辺回路が全部ISAバスにつながっている構造だったが、この構成ではCPUを高速化するとアクセスが間に合わなくなる。そこで80386が登場してしばらく後に、プロセッサーがつながる内部バスと、周辺回路をつなぐI/Oバスを分離しようという方向性に変わってくる。

図2は486のケースであるが、内部バスにはキャッシュ/DRAMコントローラーのほか、ISA Bus Bridgeがつながり、周辺回路は全部ISA Bus Bridgeの先に追いやられる形になった。この内部バスとI/Oバスの分離は、486の世代でかなり進化する。

上の図2は典型的な486マシンの構成だが、CPUから出るプロセッサーバスにキャッシュ/メモリーコントローラとISA Bus Bridgeがつながり、周辺機器は全部ISA Bus Slot側に追いやられる形になる。もっとも、486の時代にはこのプロセッサーバスをそのまま拡張バスとする「VL-Bus」という規格がVESAで制定「されてしまい」、ここにグラフィックスカードなどのI/O Deviceがつながったので、完全な分離というには十分ではなかった。

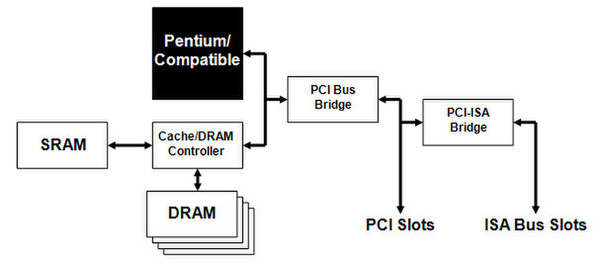

これが完全に分離されるのは、高速I/Oバスである「PCI」が登場してからで、図3の様な構造になる。つまりプロセッサーバスにはDRAM/キャッシュコントローラーとPCIバスブリッジのみが接続され、グラフィックスカードを始めとする高速デバイスは、全部PCIバスにぶら下がるようになった。低速デバイスはさらにPCI-ISAバスブリッジ経由で、ISAバスの先にぶら下がるという形だ。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ