前回のまとめに引き続き、今回よりインテルチップセットのロードマップを解説する。が、その前にまず「チップセットとはなんぞや」、という話を簡単に触れておく。

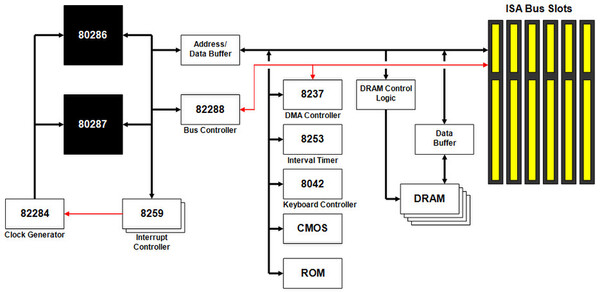

下の図1は、IBM PC/ATの内部構成をだいぶ簡略化したものである。この当時、PC/ATを構成するには7つのチップと、DRAMコントローラーやそのほかの周辺回路が必要であり、これらは独立したチップを使っていた。構成部品はかなり多かったわけだ。

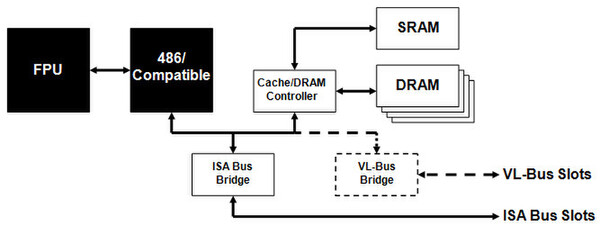

これがIntel486プロセッサーの時代になると、高性能化やデザインの容易さを考えて、だいぶ様相が変わった。図1では、メモリーを初めとする周辺回路が全部ISAバスにつながっている構造だったが、この構成ではCPUを高速化するとアクセスが間に合わなくなる。そこで80386が登場してしばらく後に、プロセッサーがつながる内部バスと、周辺回路をつなぐI/Oバスを分離しようという方向性に変わってくる。

図2は486のケースであるが、内部バスにはキャッシュ/DRAMコントローラーのほか、ISA Bus Bridgeがつながり、周辺回路は全部ISA Bus Bridgeの先に追いやられる形になった。この内部バスとI/Oバスの分離は、486の世代でかなり進化する。

上の図2は典型的な486マシンの構成だが、CPUから出るプロセッサーバスにキャッシュ/メモリーコントローラとISA Bus Bridgeがつながり、周辺機器は全部ISA Bus Slot側に追いやられる形になる。もっとも、486の時代にはこのプロセッサーバスをそのまま拡張バスとする「VL-Bus」という規格がVESAで制定「されてしまい」、ここにグラフィックスカードなどのI/O Deviceがつながったので、完全な分離というには十分ではなかった。

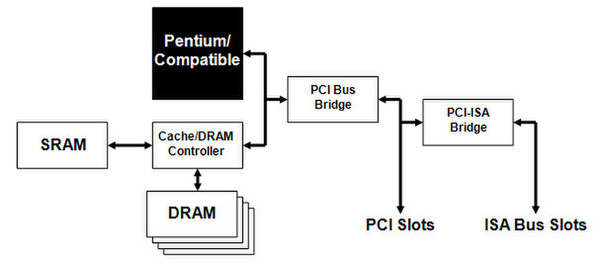

これが完全に分離されるのは、高速I/Oバスである「PCI」が登場してからで、図3の様な構造になる。つまりプロセッサーバスにはDRAM/キャッシュコントローラーとPCIバスブリッジのみが接続され、グラフィックスカードを始めとする高速デバイスは、全部PCIバスにぶら下がるようになった。低速デバイスはさらにPCI-ISAバスブリッジ経由で、ISAバスの先にぶら下がるという形だ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ