日本アルテラ(株)は2日、新アーキテクチャー“ALM(Adaptive Logic Module)”を採用した90nmプロセスのFPGA(※1)ファミリー“Stratix II”を発表した。同日、都内のホテルで記者発表会を開催し、日本アルテラ代表取締役社長の日隈寛和氏が、2003年度の実績と2004年度の方向について述べ、プロダクト・マーケティング マネージャーの堀内伸郎氏が製品の説明を行なった。製品のサンプル出荷は第2四半期の予定。

※1 FPGA(Field Programmable Gate Array) :ASIC(特定用途向けIC)の一種で、ユーザーが設計した回路を電気的に書き込んで(プログラミング)、任意の機能を持ったICを作成できるデバイス。一度書き込んだ後で再プログラミングも可能。PLD(Programmable Logic Device)とも呼ばれる。 |

|---|

| 日本アルテラ(株)代表取締役社長の日隈寛和氏 |

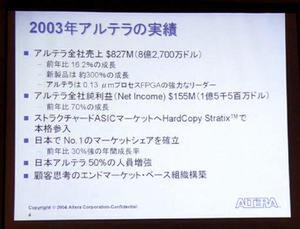

記者発表会では、最初に、代表取締役社長の日隈寛和氏が、2003年の実績と2004年の方向性について述べた。日隈氏は1月1日付けで米アルテラ社のバイスプレジデントに就任しており、米アルテラ社の2003会計年度(1月~12月)の年間売り上げが全世界で8億2720万ドル(約873億円)となり、前年比16.2%の成長をとげたこと、全社の純利益が前年比70%成長の1億5500万ドル(約163億7000万円)となったことを示した。そして、その背景には、同社が0.13μmプロセスのFPGAでリーダーとなっていること、歩留やコストダウンなど生産性の向上を挙げたほか、FPGAからASICへの移行をサポートする“HardCopy Stratix”によりストラクチャードASICの市場に参入したことなども理由として挙げた。

|

|---|

| 2003年度の実績 |

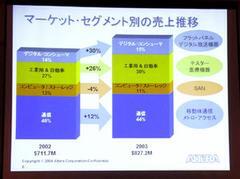

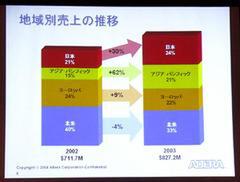

日本市場においでは、同社の成長率が30%で、各社の決算発表から計算すると日本市場でナンバーワンであったことを紹介した。地域別売り上げでは全体の24%を占め、北米に次ぐ2番目に位置しており、62%の伸びを見せるアジア・パシフィックについては、中国における製造が増えているためとした。マーケットセグメント別では、フラットパネル/デジタル放送機器向けなどのデジタルコンシューマー向けが30%増であることを示した。また、顧客サポートが重要と考え、エンドマーケット指向の組織を構築するため人員を50%増強したことを紹介した。

|

| |

|---|---|---|

| マーケットセグメント別売り上げ | 地域別売り上げ | |

| 売り上げ推移 | ||

今後の企業方針として、日隈氏は、“実行力”、“製品のリーダーシップ”、“顧客思考”を3つの柱として挙げた。“製品のリーダーシップ”に関しては、2003年度は売り上げの22%を研究開発費に割り当てており、今年は数多くの新製品を投入するとした。“顧客思考”では、さらに顧客のニーズにあった製品やサービス、サポートを提供すると述べた。

続いて、日本アルテラのプロダクト・マーケティング マネージャーである堀内伸郎氏が、新製品“Stratix II”について説明した。

|

|---|

| プロダクト・マーケティング マネージャーの堀内伸郎氏 |

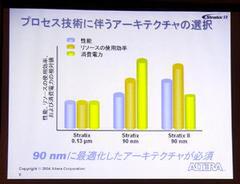

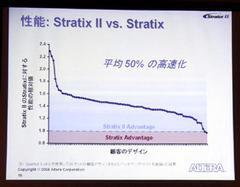

“Stratix II”は、従来の“Stratix”の後継製品で、0.13μmから90nmプロセスに微細化することで集積度を2.25倍に高め、コストを約半分に下げたほか、動作周波数の高速化で50%の性能向上、DSPの数を4倍に増やしたといった特徴に加え、新たに新アーキテクチャー“ALM(Adaptive Logic Module)”を採用したことを紹介した。

|

| |

|---|---|---|

| プロセス技術に最適化したアーキテクチャー | 最適な入力数 |

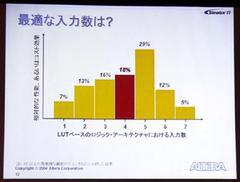

“ALM”は、0.13μmプロセスで製造されている“Stratix”のアーキテクチャーをそのまま90nmプロセスに移行すると消費電力が増えるだけでなく、高い要求にも応えられないことから考えられたアーキテクチャー。市場の95%を占める従来のFPGAでは、4入力(固定)の“LUT(Look Up Table)”が8年くらい前から使われているが、これは当時のFPGAの集積度やアーキテクチャーにおいて、性能/コストとの関係で最適だったことからきているものという。

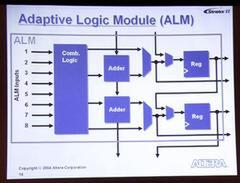

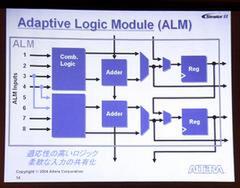

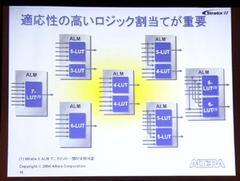

そこで、同社が現在の高集積の顧客デザインを基に分析したところ、LUTベースの入力数が最も多かったのが5入力の29%、4入力の18%となっており、6入力まであれば95%のデザインをカバーできる結果が得られたという。ここで、4入力のファンクションを4入力のアーキテクチャーで処理するなら、4入力の4本を利用すればLUTの使用率は100%だが、5入力で4入力ファンクションを処理する場合はLUT使用率が50%(32bitのうち16bitが未使用)となり、6入力ではLUT使用率が25%(64bitのうち48bitが未使用)となってしまう。そこで考えられのが“ALM”で、入力は8入力となっているが、これをそのまま使うだけでなく、4入力+4入力や、3入力+5入力のように分割して割り当てることができるようにするとともに、さらにそれらの入力同士を組み合わせて共有することもできるのが最大の特徴。これにより性能が向上したのみならず、ロジックリソースの使用効率も高くなり、複雑なロジックにも対応可能になった。ロジック段数も減らせ、内部配線も少なくなるという。

|

| |

|---|---|---|

| 入力の一部を利用する従来の使い方のほか、4+4や5+3に分割して利用することでリソースを有効利用できる | 入力を共有することで適応性の高いロジックの割り当てが可能 | |

| “Adaptive logic Module” | ||

|

| |

|---|---|---|

| 適応性の高いロジック割り当て | ベンチマークの結果 |

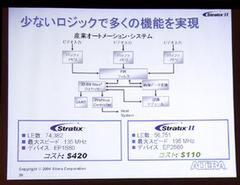

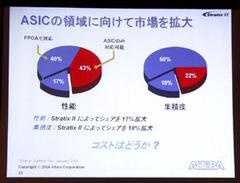

堀内氏は、次に“Stratix”と“Stratix II”の性能比較について、ベンチマークの結果では平均50%高速化されることを示すとともに、ロジック使用効率も平均1.25倍に向上すると説明した。また、少ないロジックで多くの機能を実装できることから、従来の最上位の製品をStratix IIのミッドレンジの製品で置き換えるだけで、コストが大幅に低減できることを、産業オートメーションシステムを例に示した。さらに、同社としては、従来ASICでなければ対応できなかった市場に向けて領域を拡大するとしたうえで、ASSP(特定用途向け標準品)をFPGAで置換したり、FPGAに統合することも考えていることを説明した。

|

| |

|---|---|---|

| 少ないロジックで多くの機能を実装。コストも低減できる | ASICの領域に市場を拡大 |

それに続いて、“Stratix II”のもうひとつの大きな特徴として、暗号化機能を搭載したことを紹介した。これは、FPGAのコンフィグレーション(書き込まれた回路情報)を暗号化する機能で、暗号化アルゴリズムは128bitのAES(Advanced Encryption Standard)をサポートしており、鍵の情報をチップ内部の不揮発性の領域に格納することで、コンフィグレーションが盗まれるといった心配がなくなったと説明。これにより防衛関連などの高い機密情報が求められる市場にもFPGAを提供できるようになったとした。

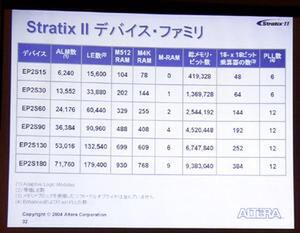

なお、“Stratix II”の製品ラインアップは、ALM数が6240の『EP2S15』から7万1760の『EP2S180』まで6品種が用意される。

|

|---|

| 製品ラインアップ |

併せて、“Stratix II”に対応した開発ツール『Quartus II Version 4.0』の提供を開始したことも発表した。既存の150を超えるすべてのIP(Intellectual Property)を利用できるという。開発キットとデモ用ボードは近日中にリリースするという。また、“Stratix II”の“HardCopy”デバイスは2005年に投入予定であることを紹介した。

|

|---|

| “Stratix II” |

本記事はアフィリエイトプログラムによる収益を得ている場合があります