富士通(株)は4日、半導体シリコンチップの厚さを従来の4分の1の25μmまで薄くする“薄化加工技術”を開発したと発表した。この技術を利用することで、複数のチップを重ねたシステムLSI(SiP:System in a Package)などの多段スタック型MCP(Multi Chip Package)の厚さを薄くできるという。また、薬液を使用しないため、チップの加工期間の短縮や、設備費用の削減、環境への配慮も行なえるとしている。

|

|---|

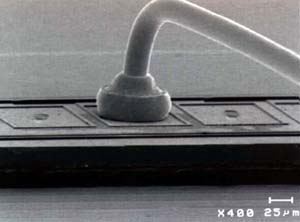

| 薄化加工技術で試作したシリコンチップ |

同社は、チップの薄化加工技術として、ウエハーサポート工法技術の開発と、ピックアップ方式の最適化を図ったという。ウエハーサポート工法技術では、半導体ウエハーの裏面研削を行なう際に、研削する半導体ウエハーをサポート治具に固定し、研削中に発生する反りを矯正して薄化を行なう。また、ピックアップ方式では、ウエハーを個々のチップに切り分けた(ダイシング)後に取り出す際に段階的に保護テープから剥離させるなどして最適化し、チップが受けるダメージを減らした。これにより厚さ25μmまで薄化加工が行なえるという。

なお、同社では、半導体研削切断装置などを開発する(株)ディスコとの技術協力により薄化加工技術を開発したとしている。