日本電信電話(株)は、単電子トランジスターを集積化し、それを組み合わせたコンピューターの基本回路を試作したと発表した。

単電子トランジスターは、通常のトランジスターが電流のオン、オフに約10万個の電子を必要とするのに対し、1個の電子で電流のオン、オフが行なえる素子。消費電力が従来と比較して10万分の1になるほか、大きさも100分の1以下にできるという。

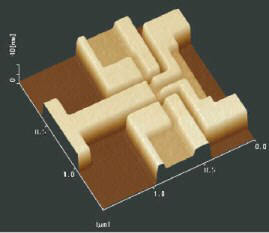

今回試作したのは、単電子トランジスターを2個並べたインバーター回路で、中核部分が0.1×0.2μm、電気的接続部分を含めても1.5μm角のサイズ。インバーターは、コンピューターの基本回路のひとつで、入力信号を逆のステート(0なら1、1なら0)に変換する否定(NOT)回路。

|

|---|

| * |

”を3次元構造に適用した“V-PADOX法(Vertical

PADOX法:ブイパドックス法)”を採用。この手法では、シリコンに浅い溝を形成し、酸素雰囲気中で温度を上げて酸化することで、単電子トランジスターが絶縁体に埋め込まれて自動的に作成されるという。

* PADOX:Pattern-Dependent OXidation('94年にNTTが考案した平面構造のシリコンを酸化させる手法)

単電子トランジスターは、従来のトランジスターとまったく異なる原理で動作するが、シリコン素材を利用し、製作手順が従来と同様であるため、既存の集積回路技術を利用できるほか、両方を混在させることも可能という。

同社では、今後、この技術を改良するとともに、より高度な機能を実現する集積回路の開発を進め、次世代の通信機器やモバイルツール、パソコンなどの開発に応用できるとしている。