限界を打破するハイブリッドボンディング

AIの進化を支えるHBM積層技術の新潮流

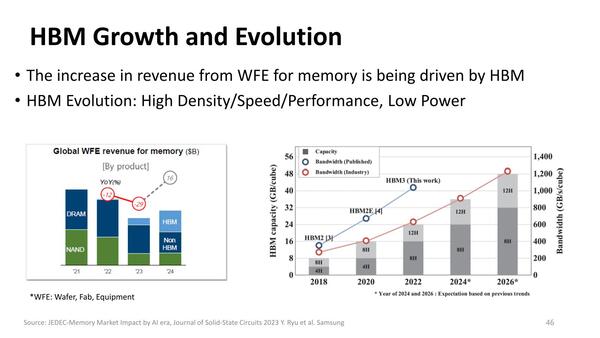

HBMといってもDRAMには違いないわけで、セルの構造の進化そのものはDRAMと違いはない。異なるのはパッケージ技術のみである。そのHBM、AIブームのおかげで猛烈な売り上げが立ち、かつどんどん高速化しているというのはご存知のとおり。

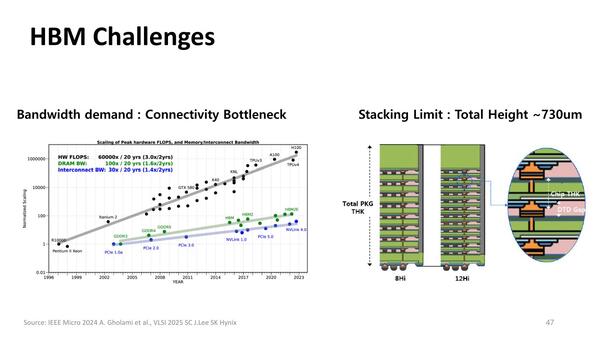

問題となるのは、より高い帯域が求められていることと、もう1つは積層数が多すぎて高さがかなりのものになっていることだ。

これは2つのデメリットがある。1つは高さがありすぎて、ASICの横に置くとASICの高さを超えてしまうこと。これは、ヒートスプレッダの工夫が必要になる。それともう1つ放熱の問題もある。HBMの場合、積層の一番下にASICとのI/Fのダイが入るが、この発熱を逃がすためには上に積みあがっているDRAMのダイを経由して放熱する必要があるのだが、層数が多くなると放熱効率が当然悪いことになる。

特にHBM3以降(3/3E/4/4E)では信号速度が高速化する分発熱量も多いので、これをなんとかしないと発熱を抑制する(=信号速度を低めに抑える)必要性が出てしまい、好ましくない。

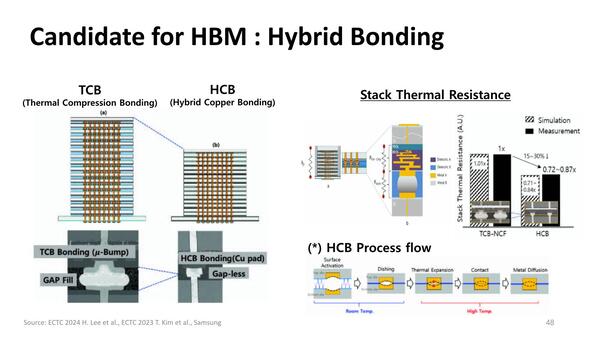

ではどうするか? というと、従来のμBumpを使った接続方式から、Hybrid Bondingに切り替えるというやり方である。

これによりμBumpがなくなる分高さを削減できるし、ついでに言えばμBumpを使った時より電気抵抗も下げられる。加えてダイ同士を極めて高密度に接触させられるので、熱抵抗も下がることになる。

実際高さが減じられたうえ、画像右にあるように熱抵抗も15~30%削減できるとしている。欠点としては、ダイを削る(右下のHCB Process flowで言えばDishingの部分)際に従来より極めて平滑度を上げる必要性がある。おそらくHybrid Bondingに対応できる新しい研磨装置と研磨材料が必要になるので、そこにコストがかかることと、その後にHybrid Bondingならではの工程が入ることだろう。

ただすでにHybrid BondingはTSMC以外にも多くの前工程/後工程企業が手掛けているので、これから手順を開発するほど手間がかかる技術ではない。わりと現実的に実用化は可能かと思われる。

ということで昨今のDRAMの進む方向性を簡単に説明した。足元では引き続きDDR5を始めとしたDRAMの入手難が続き、ついにビデオカードが入手困難、発売中止などいろいろ影響は出ているが、これはあくまでも一過性の話であり、その対応とは別に各DRAMメーカーは将来を見据えていろいろ水面下でやっている、という話である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ