低消費電力のIGZOから、積層化のVSDRAMへ

DRAMがたどり着く3D化の最終回答

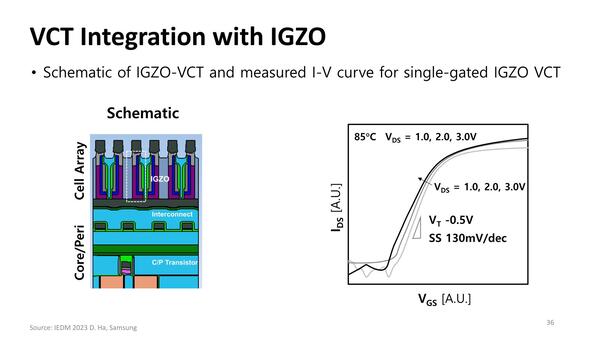

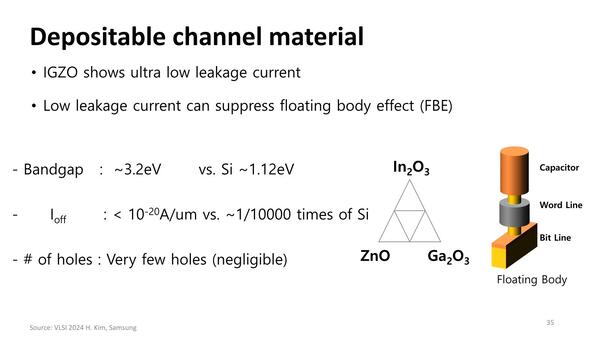

VCTに関してはもう1つ、トランジスタをIGZO(In-Ga-Zn-O)ベースのものに置き換えたIGZO DRAMの提案もなされている。2024年のIEDMで、KioxiaとNanyaが共同で開発したOCTRAMもその一例である。メリットはリーク電流の小ささで、Ioff(トランジスタオフ時の電流)がシリコンベースの現在のトランジスタと比べて劇的に減り、リフレッシュ頻度を1万分の1にできる(つまり長時間データを保持できる)点が大きなメリットとされる。

IGZO DRAM。ちなみにKioxia/NanyaのOCTRAMの場合ではIoffは10-18A、リフレッシュ頻度は1000分の1以下の100秒以上とされていた。このあたりは実装によって多少差がある

IGZOベースのDRAMは複数の実装例がすでに発表されているほか、2020年にはベルギーimecが2T0C(IGZOトランジスタ×2だけで構成され、キャパシタがない)構造のDRAMを発表するなど、今すぐ実現できるかはともかく、近い将来のDRAM用に有望視されている。

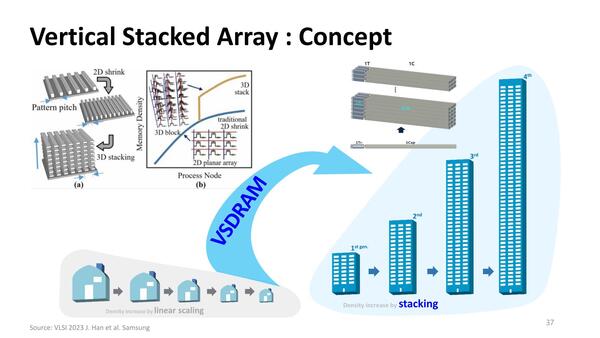

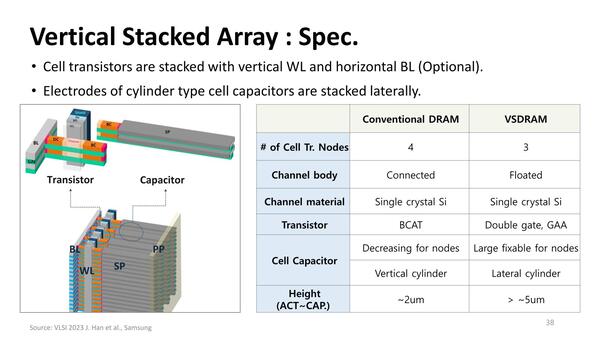

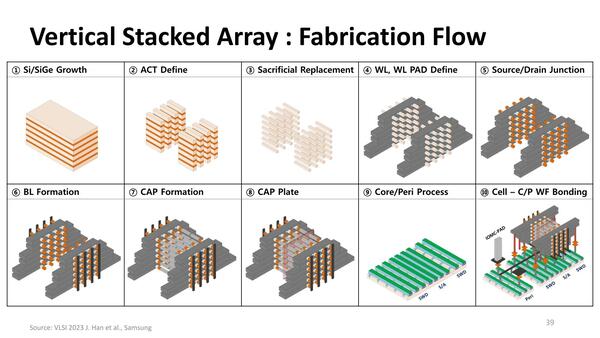

もう1つのアイディアがVSDRAMである。これ以上の微細化は無理なので、3D積層することで容量を稼ごうという、これも3D NANDフラッシュと同じ発想である。まだ多値化(SLC→MLC→TLC→QLC→PLC)に関しては研究段階で今のところ実装には至っていないが、将来的にはVSDRAMに組み合わせられる可能性がある。

話を戻すと、VSDRAMの作り方はこれも3D NANDフラッシュに似ている。DRAMセルの構造を横倒しにして積む格好である。この方式なら無理に微細化を進める必要がないので、各層の製造は比較的簡単である。このあたりも3D NANDフラッシュに似ている。

製造方法も結構似ており、まずセル・アレイ・ブロックをまとめて製造し、最後に周辺回路と合体させて完了。もちろん従来の通常のDRAMに比べれば作業工程はだいぶ増えるが、それでもHBMに比べればはるかに低コストで実現できるめどが立っているとする。

というかこれは3D NANDフラッシュの製造の経験がかなり生かされた結果だろう。NanyaやWinBondなどの3D NANDフラッシュを手掛けていないメモリーメーカーがこれを実行するのは結構敷居が高そうである

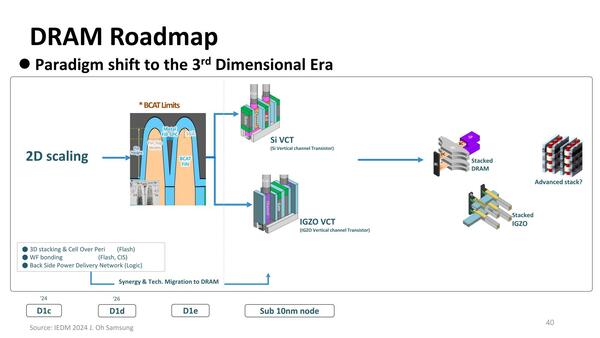

結論としては、短期的にはVCTが次の世代以降でくるが(そこにIGZOが入るかどうかはメーカー次第)、その先はVSDRAMになる、というのが基本的な方向性になりそうという見通しであった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ