MI400について

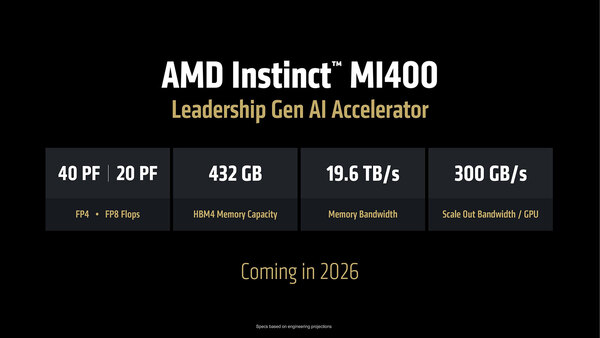

最後にMI400について同じように考察してみたい。といっても、現状で示されているのは下の画像だけである。

まずメモリー帯域。HBM4はSK Hynixが今年3月に、Micronも今年6月にそれぞれサンプル出荷を開始したことを発表している。

HBM4は信号速度は8Gbpsながら、バス幅が2048bitに拡張されたことで、1スタックあたり2TB/秒の帯域を利用できるとしている。もっともHBM3の時もそうだったが、実際にこの速度を最初の製品から出せるか? というとやや怪しく、例えば最初の製品は6.6Gbps程度でも不思議ではない。

それはともかく、トータルとして19.6TB/秒というのが曲者で、8スタックではスタックあたり2.45TB/秒が必要になって間に合わない。なので10スタック(スタックあたり1.96TB/秒)か、12スタック(スタックあたり1.633TB/秒)の構成になる。

12スタックの場合、信号速度は6.533...Gbpsということになり、これは先に示した6.6Gbpsと非常に近い。おそらくMI400の最初の製品は、12スタック/6.6GbpsのHBM4を利用するだろう。

次がメモリー容量。SK Hynix/Micronともに36GB/スタックのHBM4のサンプルを出荷しているとしており、これを12個搭載すると432GBとなるのでちょうど容量的に見合う数字になる。

性能のFP4で40PF/FP8で20PFというのはSpasity(Spasityについては連載751回を参照)の場合と考えれば、現在のMI350Xの2倍であり、おそらくMatrix Pathをさらに強化することで対応するものと思われる。そもそもHBM4を12スタック載せる時点でパッケージサイズが一回り大きくなるため、利用できるトランジスタ数は増えるし、製造プロセスはおそらくTSMC N2になる。

このN2はN3Eと比較してロジック密度が15%向上するとしており、このままではダイサイズの大型化を加味してもやや面積が足りない。ありそうなのは、HPC向けの機能はVector Pathのみにとどめ、Matrix FP64とかをバッサリ切ってトランジスタを節約するという策が講じられるかもしれない。

あと、MI350ではIODが2つだったが、MI400ではIODが3つになり、XCDの数がトータルで12などに増えても不思議ではない。問題はそのMI400の消費電力がどの程度になるか、ということだ。Rubinに負けない、2000Wクラスの製品が爆誕しそうで怖い。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ