量子誤り訂正の実証実験を本格化、6月には企業や研究機関も利用可能に

“1000量子ビット”機も間もなく 富士通・理研の256量子ビット量子コンピュータが稼働

2025年04月24日 08時00分更新

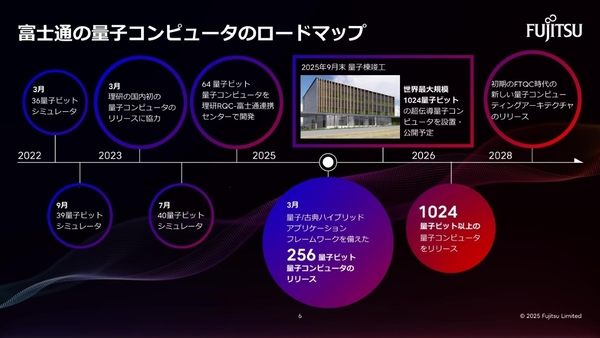

見据える未来は“beyond 1024量子ビット”

富士通の執行役員副社長 CTO システムプラットフォーム担当であるVivek Mahajan(ヴィヴェック マハジャン)氏は、稼働開始した256量子ビットの量子コンピューターも「富士通としては、あくまで全体の流れのひとつだと捉えている」と語る。

同社が見据えるのは「世界最速、最高効率」の計算技術の実現だ。そのために、量子デバイスから基盤ソフト、アプリまでの全領域で、理研を含む世界有数の研究機関と手を組んでいる。

同社では、ソフトウェア技術に注力する一方で、「最適解が分からない状態」(富士通 佐藤氏)のハードウェア技術については、幅広く可能性を追求する方針だ。実際、デルフト工科大学と共同で、ダイヤモンドスピン方式での実機開発を進めている(参考記事:量子計算エラーを0.1%未満に! 富士通がダイヤモンドスピン量子ビットで誤り訂正の実現へ)。

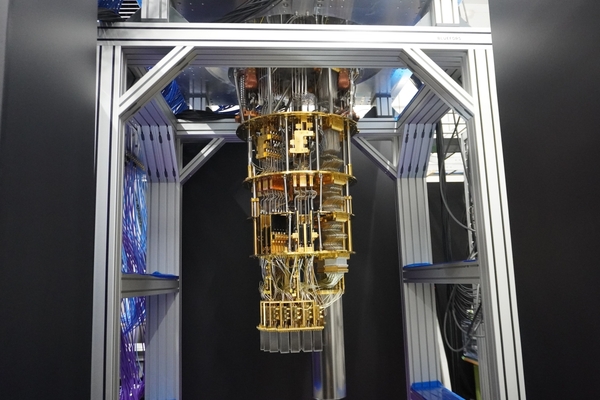

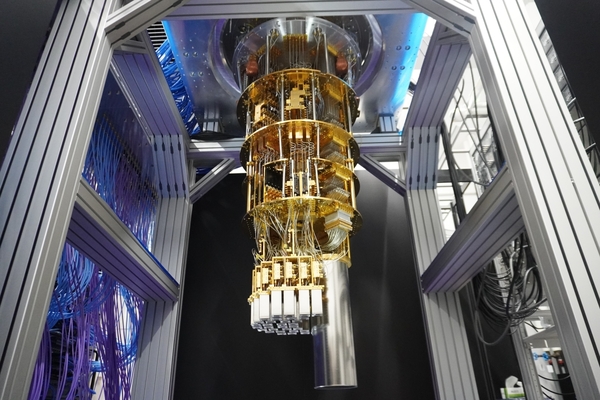

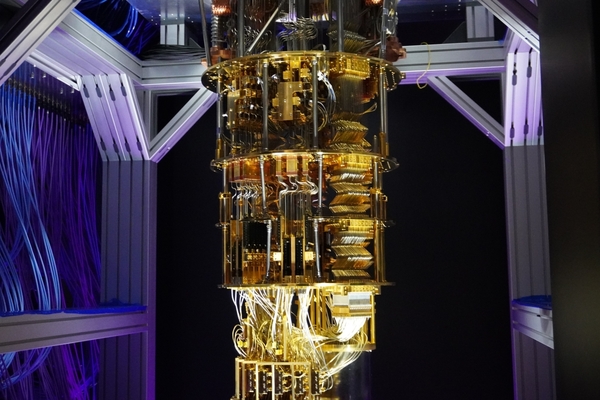

超伝導式では、連携センター発足当初から“1024量子ビット級”を見据えて技術開発を進めてきた。チップに関しては、3次元接続構造によって更なる拡張が可能で、希釈冷凍機内の高密度化も、容積と冷凍能力のさらなる増強で解決できる見込みだ。実際に、2026年には1024量子ビット機を公開することを目標としており、「Fujitsu Technology Park(神奈川県)」の量子棟に設置する予定だという。

一方で、理研側でも、チップの性能向上に重点を置きつつ、144量子ビットシステムの評価を進めるなど、独自の研究を進めていく。連携センターとしては、誤り訂正技術の実装を大きな目標としつつ、見えてきた1024量子ビット機、そして、その先のさらなる大規模化に向けた新たな技術とアーキテクチャーの創出に取り組んでいくという。

本記事はアフィリエイトプログラムによる収益を得ている場合があります