ロードマップでわかる!当世プロセッサー事情 第808回

酸化ハフニウム(HfO2)でフィンをカバーすると性能が改善、TMD半導体の実現に近づく IEDM 2024レポート

2025年01月27日 12時00分更新

インテルがHfO2成膜を実現

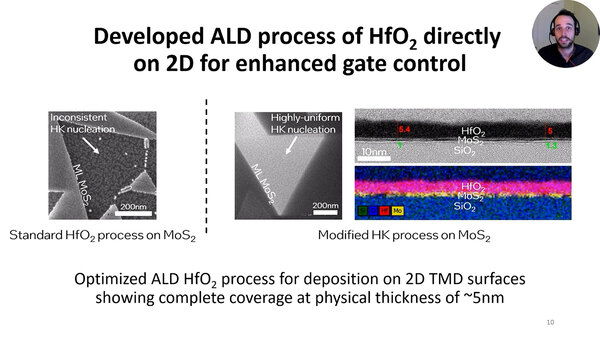

ここからが今回の発表の内容である。従来のMoS2にHfO2を積層するプロセスでは、Dangling Bond(原子における未結合手)が存在せず、このためHigh-Kでの膜形成が難しかったため、Low-Kでの膜形成層が必要になっていた。

ところがインテルは今回、HfO2 ALDプロセスを改良し、原子レベルでシャープな界面を持つ、均一でピンホールのないHfO2成膜を実現したとする。これによりLow-Kの膜を入れる必要がなくなり、それだけ特性が改善されるとする。

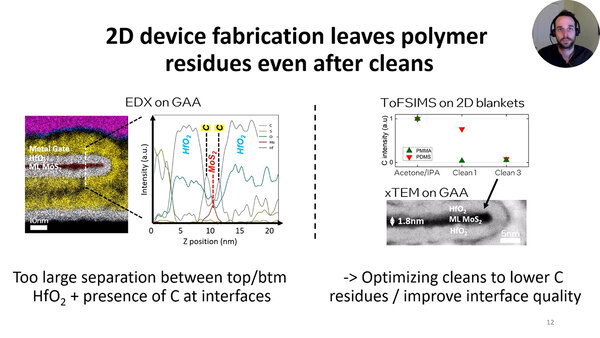

この技法を利用してGAAのフィンを構成したのが下の画像だ。厳密に言えばまだこれはGAAを構成する途中である。左はMoS2のシートの周囲にHfO2の膜を形成した状態だが、まだ周囲に炭素が大量に残っている。これを洗浄などによりキレイに取り除いたのが右の状態だ。

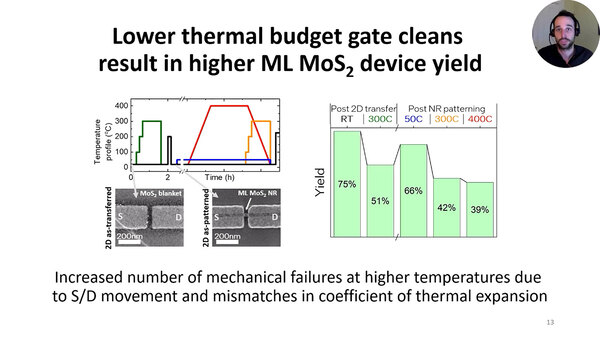

ちなみにこの洗浄の行程についても比較しており、摂氏50度という低温での洗浄でもGAAの歩留まりはわりと高い数値(66%)を維持できる一方、温度を上げるとチャネルの機械的な欠陥、あるいは剥離に起因するOpen Channel(つまりチャネルが構成できなくなる)の頻度が2倍以上に上がったそうだ。

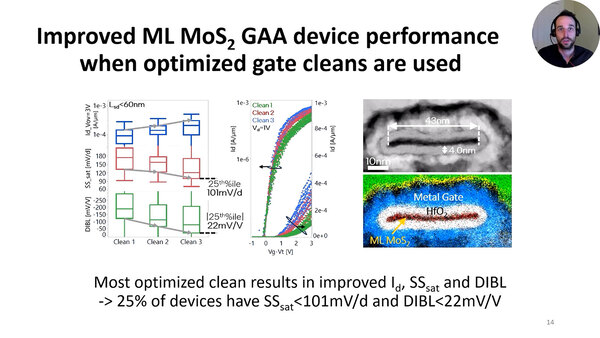

この工程を経て最終的に構築されたGAAが下の画像である。左のClean 1とClean 2は従来発表されてきた研究の際のもので、Clean 3が今回の研究の成果である。

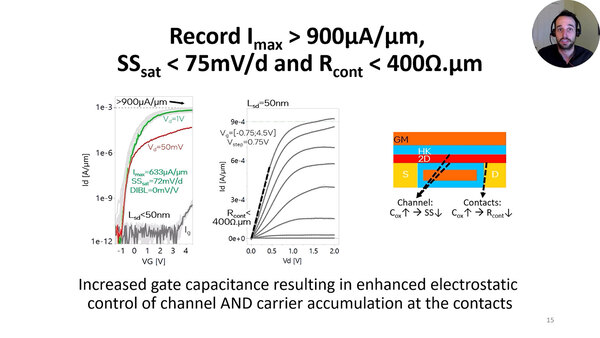

Clean 1/2と比較した場合、Clean 3のSSsatは121mV/dから101mV/dに減少し、それでいて3Vの固定オーバードライブにおける駆動電流は197μA/μmから297μA/μmとおよそ1.5倍に向上している。DIBLは111mV/Vから76mV/Vに減少している。

インテルはこの効果はHfO2/MoS2/HfO2界面の清浄度/品質の改善によるものと考えているとのことだ。

Vd=1Vにおける電流値は900μA/μmを超えており、これは記録的な数値とのこと。またコンタクト部の抵抗も記録的に少なくなっており、これらはいずれも界面の清浄度や品質の改善によって実現した、としている

ちなみにコンタクト部の抵抗Rcの数値は、大規模なGAAデバイスがまだ存在しないので直接測定できず、Vd/Id(電圧/電流カーブ)からの推定とのことだが、インテルによればこれは蒸着コンタクトスタックの最適化値に近いとしている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ