ロードマップでわかる!当世プロセッサー事情 第786回

Xeon 6は倍速通信できるMRDIMMとCXL 2.0をサポート、Gaudi 3は価格が判明 インテル CPUロードマップ

2024年08月26日 12時00分更新

前回でXeon 6についての解説はおおむね終了しているが、2つほど細かい話が抜けているのでその補足をしつつ、最後にGaudi 3の情報アップデートについて説明する。

Xeon 6向けのMRDIMMが出荷開始

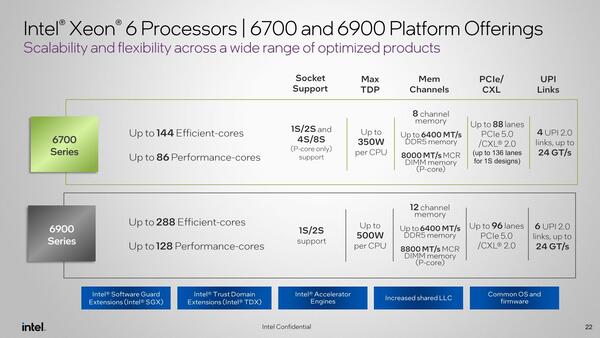

連載785回にもあるが、Xeon 6世代ではDDR5で最大6400MT/秒をサポートするのに加え、MCR DIMMのサポートがあり最大8800MT/秒に対応するとされる。

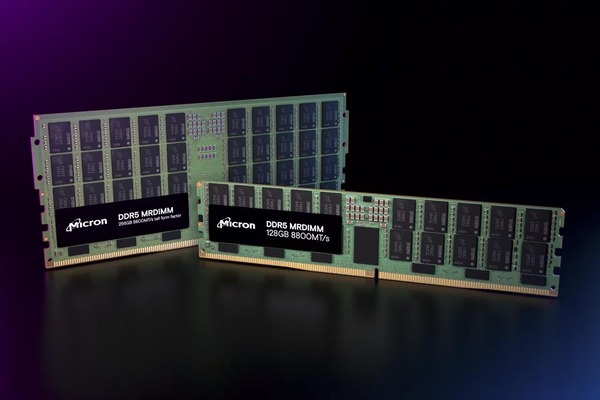

この説明はCOMPUTEXのタイミングなので6月第1週だったが、6月16日にMicronはXeon 6向けにMRDIMMのサンプル出荷を開始した。量産出荷は今年後半を予定していることも発表された。

MicronのMRDIMMページより。左がFull Height、右がHalf Heightだそうだ。Halfでも通常のDDRより背が高そうだ

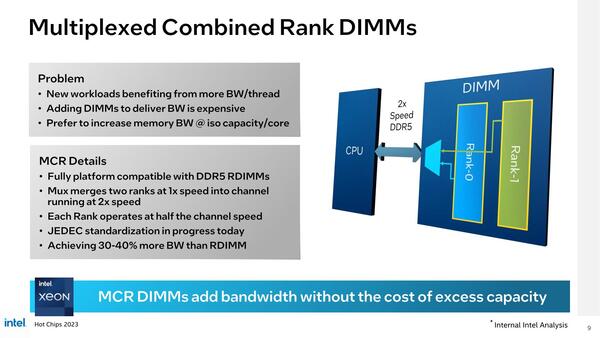

MRDIMM、あるいはMCR DIMMと呼ばれるものの仕組みは連載723回で説明している。連載736回で示した下のスライドの方がわかりやすいかもしれないが、従来Registered DIMMと呼ばれていたものはクロック信号、Address/Command、データという3種類の信号すべてについてDIMM上に置かれたレジスター(要するにバッファである)を介することで、信号の波形の乱れをレジスターで補正できるため、安定してDRAMチップとの通信が可能になるというものである。

このレジスターを改良というか魔改造(?)し、ホストとの間を倍速で通信できるようにするとともに、Rank 0/Rank 1の両方のDRAMチップに対してインターリーブ的に通信できるようにしたのがMRDIMMである。最初のMRDIMMは8800MT/秒となっているが、これはホストとレジスターの間の速度であり、レジスターとRank-0 DRAMあるいはRank-1 DRAMの間は4400MT/秒となる。

これにより、転送速度が従来のDDR5-4400の倍になるほか、1枚のDIMMに搭載できるRankの数を倍増できるので、DIMMあたりの容量も大きくできる(その分DIMMも大型化するが)。ただし現状でもDDR5で複数枚のDIMMを装着すると転送速度が4400MT/秒あたりに落ちる。というより、これを超えると安定して動作しないため、MRDIMMを利用する場合も当然1chあたり1枚となる。

実質的には従来2枚のRegistered DDR5 DIMMを1枚のMRDIMMに置き換えることになるため、トータルでの容量そのものは増えないかもしれない。

なおMCR DIMM(Multiplexer Combined Ranks DIMM)と称しているのはインテルだけで、他社はすべてMRDIMM(Multi-Capacity Rank DIMM)と称しており、内容は変わらない。したがって以下はMRDIMMで統一する。

さてこのMRDIMMだが、実は主要なFCLGA4677対応のサーバー向けマザーボードは半分くらいは1 DIMMスロット/チャンネル構成になっている。ただ残りの半分は2 DIMMスロット/チャンネルである。例えばSuperMicroのHyper SuperServer SYS-221H-TNRの場合、Socket 1つあたり16本のDIMMスロットが装備されている。

ところがMRDIMMの場合、仮に使っていなくても空きのDIMMスロットが配線上にあるだけで信号波形の乱れにつながるためか、基本1 DIMMスロット/チャンネルでないときちんと動かないらしい。今回ソケットをFCLGA 4677からFCLGA 4710に変更した理由は、既存のFCLGA 4677のままでは2 DIMMスロット/チャンネルのマザーボードでMRDIMMがきちんと動かないから、というあたりもあるのではないかと筆者は疑っている。

下の画像についてもう1つ話がある。Mem Channelの所を見ると、通常のRegistered DIMMに関しては6400MT/秒までであるが、問題はMRDIMMについてである。

そもそもMRDIMMをサポートするのはPコアのXeon 6のみ。つまりGranite Rapidsのみとされている。これはXeon 6700、すなわちFCLGA4710だけでなくFCLGA 7529(と言われている巨大なソケット)のXeon 6900も同じであり、要するにSierra Forest用のコンピュート・タイルに搭載されたDDR5のメモリーコントローラーはMRDIMMのサポートが省かれているらしい。

これは正直理解できない話で、いくらPコアに比べて性能が低めといっても、Xeon 6900の方のSierra Forestは最大288コア/576スレッドであることがすでに発表されている。

Xeon 6900だから12chのDDR5 I/Fを持つが、DDR5-6400のピーク値でも最大で614.4GB/秒。コアあたりで言えば2.1GB/秒程度、スレッドあたりで言えば1GB/秒そこそこでしかない。こういう比較が正しいかどうかわからないが、例えばAtomベースのIntel N100ですら4コアに対してDDR5-4800が提供されるから、コアあたりの帯域は9.6GB/秒はある計算で、本当にこれで十分な帯域なのか? は正直理解できない。

MRDIMMをサポートしたとしてもコアあたり2.93GB/秒程度、Threadあたりで1.5GB/秒弱でしかないから、サポートしてもたいして性能改善につながらない、という考え方もあるのかもしれないが。

また6700シリーズのPコアは最大で8000MT/秒というあたり、おそらくLCCのコアに搭載されたメモリーコントローラーは8000MT/秒止まりで、8800MT/秒はHCC/XCCコアのみのサポートだろう。技術的な問題というよりは、製品グレードによる差別化が主な目的であるように思われる。

この連載の記事

-

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 - この連載の一覧へ