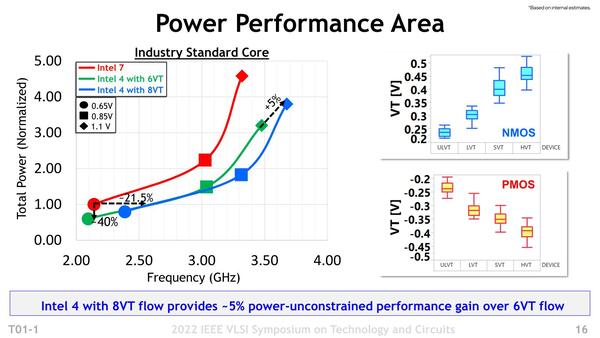

性能はIntel 7より21.5%向上

次は性能について。冒頭で最大20%以上の動作周波数向上という数字が出てきたが、その詳細が下の画像だ。Intel 7の2.1GHzにおける消費電力そのままなら2.4GHz前後、およそ21.5%の向上が可能で、同じ2.1GHzのままなら40%程度消費電力を下げられるとしている。

興味深いのは3VT(ULVT/LVT/SVT)と4VT(ULVT/LVT/SVT/HVT)の2つの電源電圧パターンを選べるということだ(図では6VT/8VTとなっているが、これはPMOS/NMOSで異なる電圧だからで、パターンとしては3種類ないし4種類になる)。

3VTの方が低消費電力に向いており、ただし動作周波数そのものは3.5GHz弱程度だからピークではIntel 7(およそ3.3GHz)に比べて6%程度の伸びにしかならない。一方4VTのケースだと、最低動作周波数は2.4GHz程度に引きあがるが、ピーク動作周波数は3.7GHzあたりまで引き上げられる。

使い方としては、モバイル向けのSKUでは3VT構成で製造することで性能/消費電力比を引き上げ、デスクトップ向けは4VT構成にすることでより高い動作周波数を狙う、というやり方が使える。

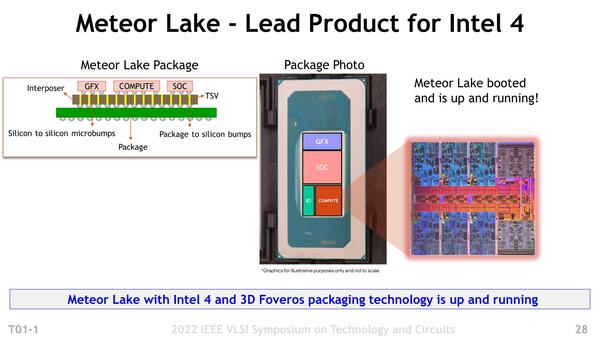

これまでのインテル製プロセッサーのダイは、モバイルとデスクトップは基本的に同じダイを共用していたのでこういうことは難しかったが、Intel 4で最初に製造されるMeteor Lakeの場合はチップレット(インテル用語ではタイル)構成になる。したがってモバイル向けのCPUタイルとデスクトップ向けのCPUタイルを分けることそのものは難しくないだろう。

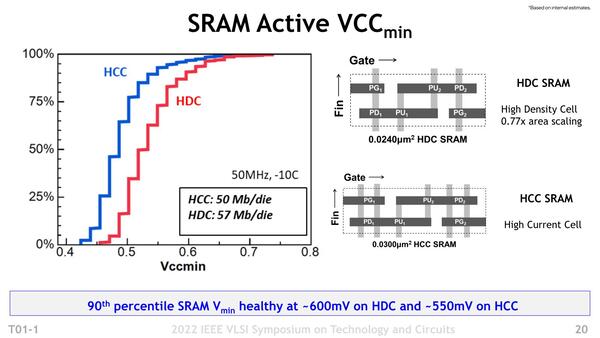

2次/3次キャッシュなどで多用されるキャッシュに関しても説明があった。こちらもHigh Density(HDC)とHigh Current(HCC=High Speed)の2種類のSRAM CELLが用意されるとする。

HDCはFinの数を2本減らしており、これがそのまま電流削減→速度低下につながる一方で、密度そのものは下げられる。ちなみにこの図はこれ全体でSRAMセルなのではなく、SRAMセルを構成するトランジスタの構造であって、実際はもっと大きい

HCCが基本となるSRAMセルで、0.03μm2。こちらは高速向けなのでコア内のレジスターファイルや0次/1次キャッシュなどに使われる格好だ。

一方HDCは電流を抑えたやや低速向けで、2次/3次キャッシュに使われることになるだろう。HDCは0.55V、HCCは0.6Vおよそ9割のSRAMセルが正常動作するとしており、実際には0.6V~0.65Vあたりでの駆動になると思われる。

最後が、これは配線層に属する話だが、MIMキャパシターの話である。インテルは10nm SuperFinの世代でSuper MIM Capacitorと呼ばれる新しいコンデンサーを配線層に埋め込んだことを発表した。Intel 7でもこのSuper MIM Capacitorをそのまま利用していると思われるが、Intel 4ではこの容量をおおむね倍増させたとしている。

コンデンサーがあるとなにが良いか? であるが、1つはアナログ回路を構築するのに便利、もう1つはパスコンとしての役割である。パスコンの効果は連載658回のBOW プロセッサーのところでも説明したが、回路に近いところにパスコンを置くことで動作速度を引き上げることが可能になる。もちろんBOWプロセッサーほどには容量がないものの、Intel 7に比べると若干改善しているのは間違いない。

この図が正しければモバイル向けのトップエンドはP-Core×6+E-Core×8になる。一説によればP-Core×6+E-Core×4+Low Power E-Core×4、という話もあるが、そのあたりの真偽は現時点でははっきりしない

ということで良いこと尽くめに見えるのがIntel 4であるが、肝心の歩留まりに関しては相変わらず黙秘のままである。Meteor Lakeについても、完成して正常に起動、動作しているという説明を信じれば「ちゃんと作れたものはちゃんと動く」というわけだ。

ただ問題は「どれだけちゃんと作れるの?」というあたり。インテルの説明によれば、今年後半にIntel 4の量産に入るという話だが、昨今流れている情報ではMeteor Lakeの投入は2023年後半になるとされる。いくらなんでもリードタイムが長すぎないか? というのが率直な疑問で、逆に言えばそれほどリードタイムが必要なくらい、Intel 4の歩留まりは低い可能性もある。まだまだIntel 4の動向を注視していく必要がありそうだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ