ロードマップでわかる!当世プロセッサー事情 第655回

Alder Lakeと十分戦える省電力機能が実装されたRyzen 6000 Mobileシリーズ AMD CPUロードマップ

2022年02月21日 12時00分更新

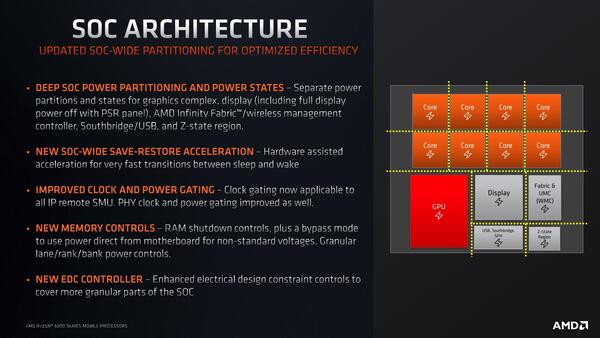

次にSoCレベルでの工夫についてだ。

ちなみに、GPUは一塊である。これ、以前もJoe Macri氏に聞いたことがあるが、GPUの場合はCPUと異なり、全体が連動して動くので、ここでPower GatingやClock Gatingをやっても意味がないとのこと

Deep SoC Power Partitioning and Power states

(より粒度の細かいClock/Power Gatingを可能に)

なるべく細かいブロック分けして、Clock Gating(クロックの供給停止:ダイナミックパワーがほぼゼロに近くなる。ただリーク電流に代表されるスタティックパワーは減らない)やPower Gating(電源そのものも供給停止)を実現できるようになった。

これに関しては、Z-State Regionという、システム復帰に必要なブロックにさえ電力を供給しておけば、他のブロックは全部電源供給を止めても対応できるようになっている。

New SoC-Wide Save-Restore Acceleration

(待機あるいは復帰を高速化)

CPUだけでなく、チップ全体のその他の部分でも待機状態や復帰状態に素早く入るためのハードウェア機構を追加している。

Improved Clock and Power Gating

(Gatingの粒度をさらに細かく)

例えば周辺回路ではPHYとMACを別々にClock/Power Gatingをできるようにした。PHYをPower Gatingしてしまうと、復帰の際に時間がかかる(PCIeやUSB 3以降の場合、まずLink Trainingと呼ばれる信号伝達状況の確認手順から入ることになるので、余分な時間が必要になる)一方で省電力の効果は大きいので、ニーズによってはPHYまで電源を落とした方が効果的である。このあたりのコントロールが可能になった。

New Memory Controllers

(メモリーコントローラーの省電力機能を拡充)

もともとDDR5/LPDDR5ではかなりいろいろな省電力機構が用意されているが、これに加えてDIMMをLane/Rank/Bank単位で電力制御できるようにしたほか、オーバークロック駆動のDIMMを利用する場合に向けてBypass Modeと呼ばれる動作モードも提供される。

New EDC Controller

(SoC内部への電力供給の粒度を下げた)

EDC(Electrical Design Constraints)というのは、SoC内部のブロックに対する電力供給であるが、これを一律にするのではなく、ブロックごとに細かく最適な電圧にすることで、無駄を減らした。

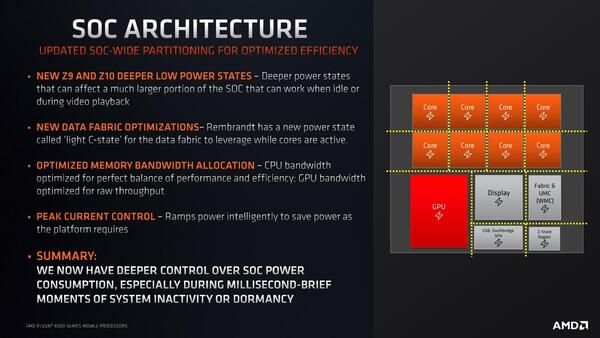

New Z9 and Z10 Deeper Low Power State

(新たにZ9/Z10という動作モードを追加)

例えばDVDの鑑賞などでは、SSDからデータブロックを読み出してそれを内蔵デコーダーで展開、画面出力するだけでいいので、CPUを含むほとんどのブロックは稼働している必要がない。こうした使い方に向けて、チップのほとんどを休止状態とするモードを追加した。

New Data Fabric Optimization

(インフィニティー・ファブリックに省電力モードを追加)

先にCPUのところに出てきたCCX Light C-Stateと対になる機能で、インフィニティー・ファブリックに省電力モードが追加された。これにより、完全にスリープするほどではないけど一時的に転送がなくなった時などに省電力効果が高められる。

Optimized Memory Bandwidth Allocation

(メモリーアクセスの最適化)

CPUに対しては効率的なメモリーアクセスを、GPUに対しては最大の帯域を提供するようにメモリーコントローラーの動作を変更している。これにより、CPUのみを使う場合のメモリー回りの省電力化が図れる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ