HBMコントローラーをパッケージにどう収めるか?

もう1つの問題はパッケージサイズとHBMに関わる部分だ。UPIとHBM、つまりEMIBを利用して接続するI/Fに関しては、タイルの最外周に配置する必要がある。電源やDDR5に関しては、Package Substrateの中を通して引っ張り出せるが、EMIB経由ではそうした長い配線は利用できないからだ。

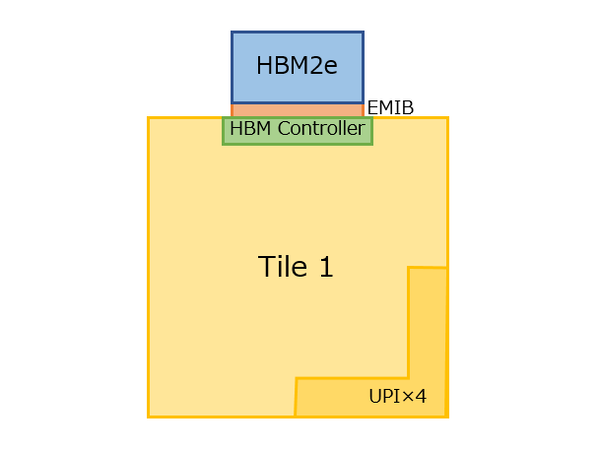

左上のものをTile 1とすると、そのTile 1におけるUPIとHBMのコントローラーの物理的な位置は下図のようになる。

HBM搭載パッケージは長辺方向がさらに伸びるわけで、するとHBM2eのスタックはTile 1の上側に位置することになる。

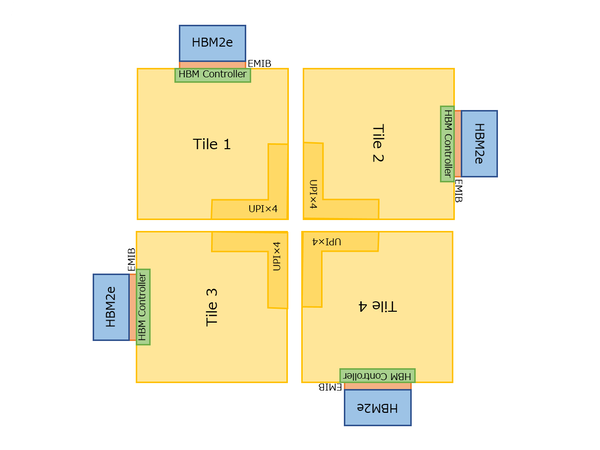

このTileを4つ並べるとどうなるか? というのが下図である。もしSPR HBMが横に広いパッケージになっていれば、図の構成は容易だ。ところが実際には縦方向に長いわけで、図の構成では問題があることになる。

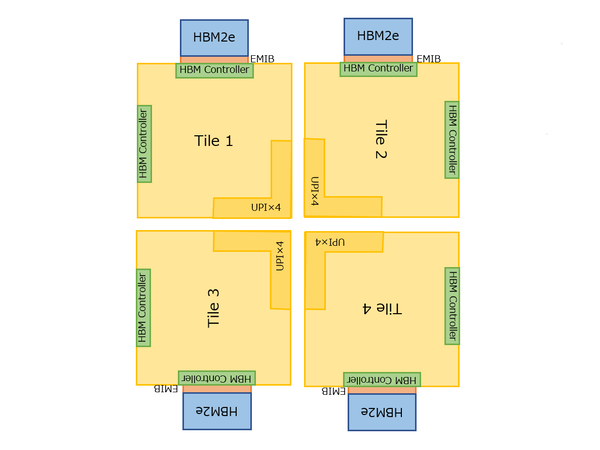

解決策は2案ある。1つはHBMのコントローラーを2つ設け、下図のようにどちらかを使う方法にすることだ。ごらんの通り、これならHBMスタックをタイルの上下に追い出せる。ただしHBMコントローラーを余分に搭載する分、エリアサイズが無駄になる。

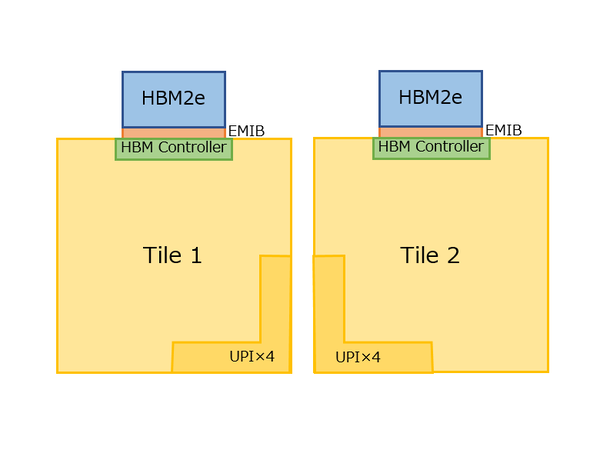

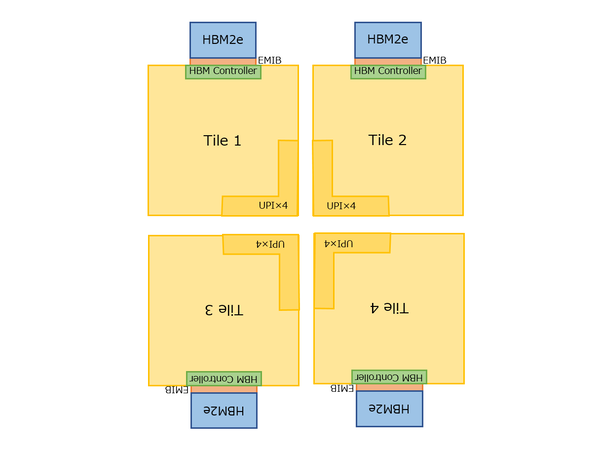

もう一つの案は、下図のように鏡合わせのように2種類のタイルを用意することだ。

こうすると、4タイルの構成も下図のようにHBMスタックを上下に追い出せ、しかも無駄な2つ目のHBMコントローラーを搭載する必要はない。その代わりに2種類のタイルを製造する必要があり、これは間違いなくコストアップにつながる。

筆者としては3つ前の画像の「2つのHBMコントローラーを搭載している」案を推したいところだが、これも正直製品が出てこないとよくわからない部分である。

なお、カンファレンスにおける質疑応答としてもう1つ明らかになったのは、Sapphire Rapidsは4本のUPI Linkを外部に出すほか、DDR5は8chと説明されているが、これはトップエンドのSKUのみならずそれ以下のSKUでも共通する。

同じ問題は第1世代EPYCでも存在しており、それもあって第1世代EPYCは有効コア数が少ないSKUであっても4ダイ構成を取ることになっていたが、同じようにSapphire RapidsもすべてのSKUでタイルは4つなのか、あるいは実は今は1タイルとして示しているものが、実際にはCPUコアやLLC、アクセラレーターを搭載したタイルとDDR5/UPI/PCIeを搭載したタイルの2つに分かれており、間をEMIBでつなぐという話なのか、もしくは低コア向けにはメモリーコントローラーやPCIeを倍量搭載するタイルが用意されているのか。いろいろと謎は尽きない(むしろ謎が深まった)のが現時点でのSapphire Rapidsの状況である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ