第2世代EPYCプロセッサーを発表

7月に第3世代RyzenとNAVI 10ベースのRadeon RX 5700シリーズが発売されたわけだが、これに続き8月7日に第2世代EPYCプロセッサーが発表された。速報記事もあるが、それより細かく説明したい。

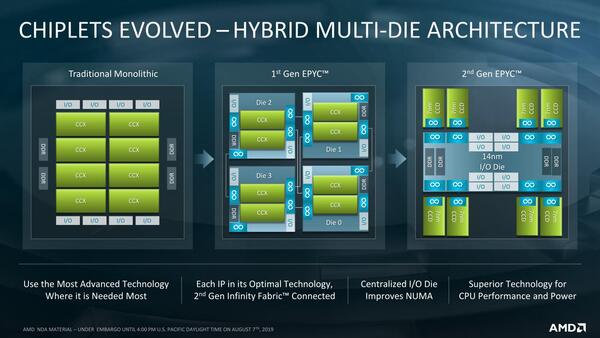

第2世代EPYCは、Zen2コアのCPUチップレットを最大8個と、14nmで製造されるI/Oチップレットを搭載する9コアのMCM構成である、という話は昨年11月に連載484回で解説した通りである。

コアそのものはRyzen 3000シリーズと同じZen2コアなので、第516回で説明した内容はそのまま第2世代EPYCにも通用する。

異なるのはI/Oチップレットの構造である。実はこのI/Oチップレットに関しては完全にはすべての構造が説明されているわけではない(8月18日~20日に開催されるHotChips 31でAMDも講演を予定しているので、あるいはここで詳細が語られるかもしれない)のだが、一応今回説明されている範囲で解説しよう。

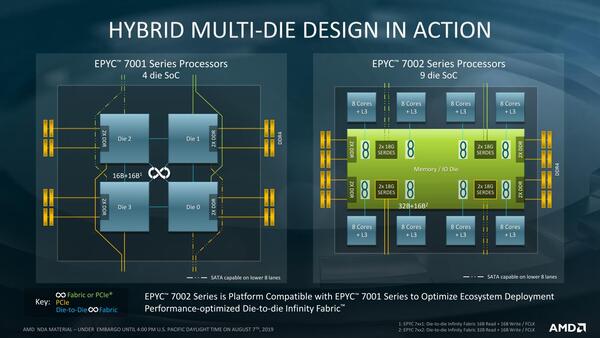

まず下の画像が9ダイの接続図である。ポイントは3つ。

1)I/OチップレットとCPUチップレットの間のリンクは48Byte/サイクルのインフィニティー・ファブリックで接続される。このリンクの速度はFCLKで決まる。

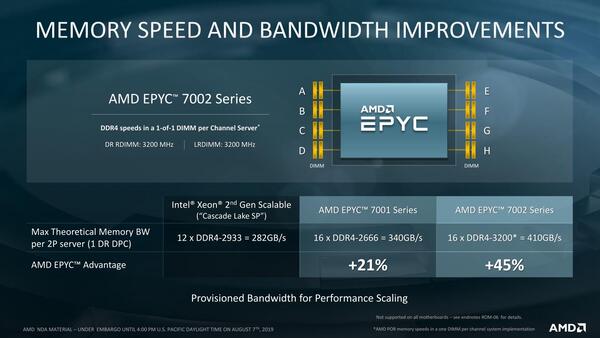

Ryzenの例で言えば、DDR4-3733まではMCLKと同期するという話であり、DDR4-3200を利用する場合であれば800MHzとなり、帯域は38.4GB/秒(リード25.6GHz+ライト12.8GHz)となる計算だ。初代EPYCではリード/ライトともに最大でも10.67GHz(DDR4-2666対応)だったので、合計でも21.3GB/秒でしかなかった。

2)Socket構成の場合、初代EPYCはPCI ExpressレーンのPHYを転用する形で接続することになっていたが、第2世代EPYCでは18GT/秒×2の接続用PHY(各々16レーン)が4ch用意される。うち2つはSATA接続も兼用しているので、必ずしも全レーンを利用しない場合もあるが、仮に全レーンを接続に利用した場合、18G×2×16レーン×4ch=288GB/秒もの帯域で接続されることになる。

3)DDR4は8chのまま据え置きである。ただ、初代EPYCの際には、市場に出ている最大容量のDRAMチップは8Gbitで、両面実装にしてDIMMあたり最大でも128GB。これを8ch/16スロットにフルに埋めると2TBが最大であった。ところが現在は16Gbitチップが出荷開始されており、これを利用すると同じ8ch/16スロットでも最大で4TBの容量が可能になる。これを前提に、最大容量は4TBとされている(*1)。

ところで最後のメモリーの件、連載第484回で16chにするのでは? と予測したのだが、意外にも8chで据え置きであった。

これについてはイベント後の質疑応答の際にダイレクトに「なぜ16chにしなかったのか」と聞いたのだが、「なぜ16chにしなかったのか」に対する直接的な答えはない代わりに「8chといってもメモリー容量は倍になり、スピードもあがり(DDR4-2666→DDR4-3200)、なにより3次キャッシュの容量がトータルで4倍になった。これのお陰で、DDR4のチャネルを倍増しなくても十分に性能が確保できている。実際ベンチマーク結果を見ると(コア数に応じて)性能がスケールしている」という返事であった。この性能の話は後述する。

(*1) 後で確認したところ、初代EPYCでもBIOSアップデートをかければ技術的には4TBメモリーを利用可能とのこと。技術的には、というのはマザーボードメーカーがそうしたBIOSをリリースするかどうかは不明だからとのこと。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ