USB 3.2で配線が大幅に変更

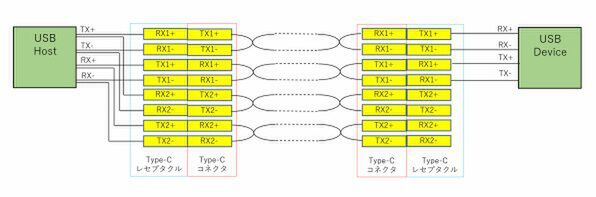

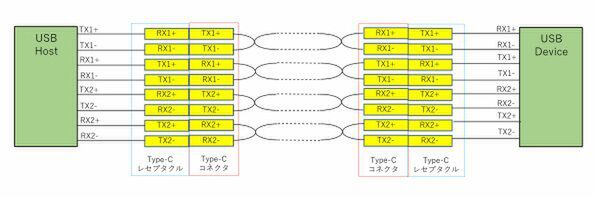

USB 2.0/3.0/3.1についてはそもそも信号が1セット分しかない。このため配線は下図のようになっている。

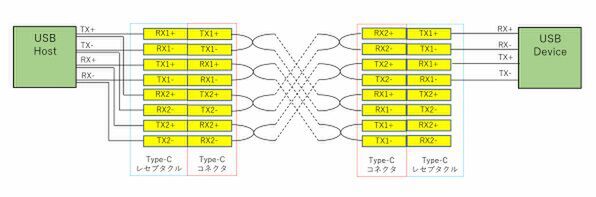

USBホストは、接続時にTX1/RX1とTX2/RX2のどちらにUSBデバイスがつながっているかを検知し、つながっている方と通信するという仕組みだ。上図の場合はTX1/RX1側を利用して通信するわけだが、下図のように仮にデバイス側のコネクターが裏返しに差されていた場合、今度はTX2/RX2側を利用して通信する仕組みとなる。

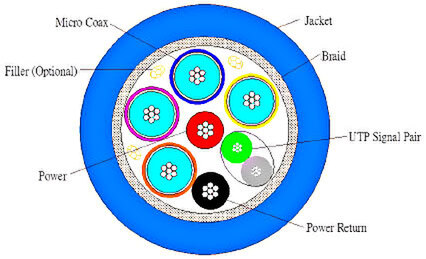

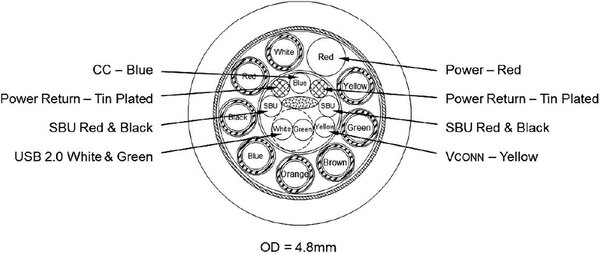

そこで配線そのものも大幅に変更になった。下の画像はStandard/Micro USBと、USB Type-Cケーブルの断面図であるが、配線そのものが大幅に増えているのがわかる。

画像の出典は、USB 3.1 Legacy Cable and Connector Specification Revision 1.0

さて、話はUSB 3.2である。USBは2レーンオペレーションと言っており、要するにこれからは下図のようなつなぎ方になるわけだ。

コネクターが裏表逆になると、その側はTX1とRX2/TX2とRX1がそれぞれつながるような形になるが、もともとTX1/RX1とTX2/RX2は単に配線などの都合上番号を振っているだけで、必ずしも1と1がつながらなくても問題はない。ただこうした構成にしたことで、コントローラーの構造に変化が生まれることになった。

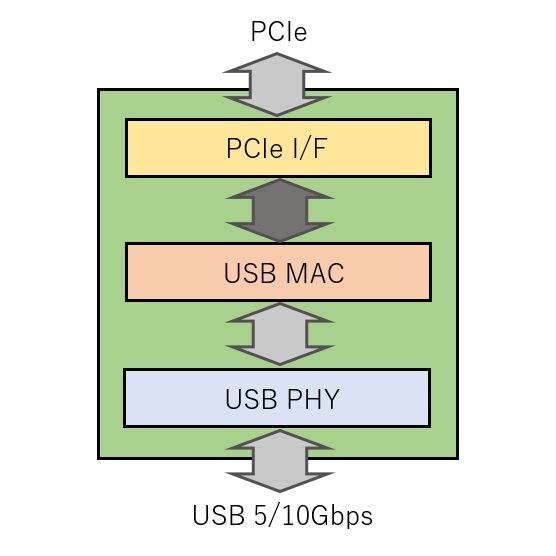

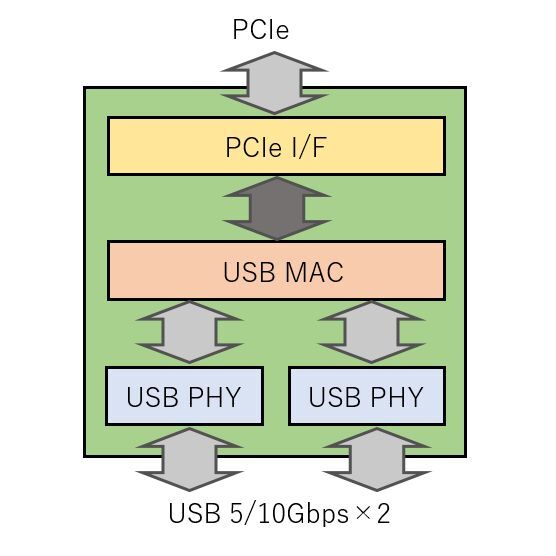

下図は従来のUSB 3.1までの構造である。ホスト(CPUなりチップセットなり)とPCIeのI/FでまずUSBのMAC層がつながり、その下にPHY(物理層)がつながり、その先にUSBが出てくるわけだが、USB 3.2の2レーンオペレーションでは、PHYが2つという構成になった。

信号速度は相変わらず5Gbpsないし10Gbpsであるが、それが2組出る形だ。ちなみにUSB 3.1までの互換モードで動作する場合、2組のPHYのうちの片方のみが動作し、片方は休んでいる状態となる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ