2013年にUSB 3.1の規格を解説したが、そこからすでに6年。実は2017年にUSB 3.2の仕様策定は完了しているのだが、こちらはまだ普及に至ってない(コントローラーすら存在しない)のにも関わらず、先日USB 4.0の発表があったりと、急にUSBを巡る状況がさわがしくなってきた。そこで、USBの規格を改めて整理しておこう。

そもそもUSB 3.2とは?

USBの仕様策定を司るUSB-IF(USB Imprementation Forum)は2017年9月25日、USB 3.2の仕様策定が完了したことを発表した。発表によればUSB 3.2とは以下のものとされている。

- Two-lane operation using existing USB Type-C cables

(既存のUSB Type-Cケーブルを利用して、2レーンオペレーションを行なう)

- Continued use of existing SuperSpeed USB physical layer data rates and encoding techniques

(既存のSuperSpeed USBの物理層とデータレート、エンコード方式などをそのまま継承する)

- Minor update to hub specification to address increased performance and assure seamless transitions between single and two-lane operation

(1レーン/2レーン操作の移行をスムーズに行なうため、Hubの仕様は若干アップデートされた)

要するに、以下の方法で転送速度を倍にした形だ。

- USB 3.0:5Gbpsの送受信レーンを1対追加

- USB 3.1:送受信レーンを10Gbpsに増速

- USB 3.2:送受信レーンを2対に増強(速度は10Gbpsのまま)

これが可能になったのは、USB Type-Cコネクターとケーブルが、そもそも2対の信号線を持っていたためだ。USB Type-Cでは「コネクターに裏表がない」(厳密に言えばあるのだが、表裏逆に差しても送受信が問題なくできる)という仕組みを実現しているが、これを実現するために、同時に2対の信号を送受信できるようにしてある。

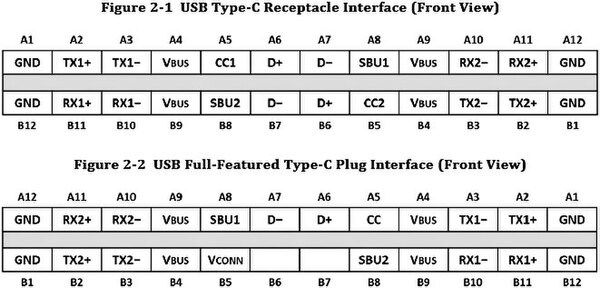

レセプタクル(Type-Cのジャック)とコネクターの配線レイアウトを下の画像に示すが、表裏(A側とB側)がちょうど180度ひっくり返ったようになっているのがわかる。

画像の出典は、Universal Serial Bus Type-C Cable and Connector Specification Release 1.3

| 信号線の意味 | ||||||

|---|---|---|---|---|---|---|

| D+/D- | USB 1.1/2.0の信号伝送用。双方向伝送。レセプタクル側(Figure 2-1)を見ると一見2対の信号が用意されているように見えるが、プラグ側(Figure 2-2)を見るとわかるように信号線そのものは1対しか用意されていない。 | |||||

| TX1±,TX2±, RX1±,RX2± |

USB 3.0/3.1用の信号伝送用。こちらは速度が高速な関係で片方向伝送となっているので、2対4本で1セットとなる。なのでここでは2セット分の配線が用意されているのがわかる。 | |||||

| VBUS | 5Vの電力供給用 | |||||

| GND | 5V電源用のGND。片面あたり2本に増えており,1本で500mA,2本あるので片面あたり1Aまで流せる。 | |||||

| SBU1,SBU2 | Type-Cで追加された追加の信号線(Side Band Use)。通常の接続では利用されないが、Type-CのAlternate ModeやAudio Adapter Accessory Modeなどではこれを利用することが規定されている。 | |||||

| CC1,CC2 | Configuration Pins。これもType-Cで追加されたもので、特にUSB PDを利用する際に電力の供給元/供給先/Dual-Role(電力の供給元/供給先のどちらにもなれるもの)の区別を行うために、このピンを利用して通信する。 | |||||

以上のようにケーブルおよびコネクターは2セット分の信号を同時に流せるようになっている。おそらくはType-Cの策定時に、Two-Lane Operationへの配慮があったのだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ