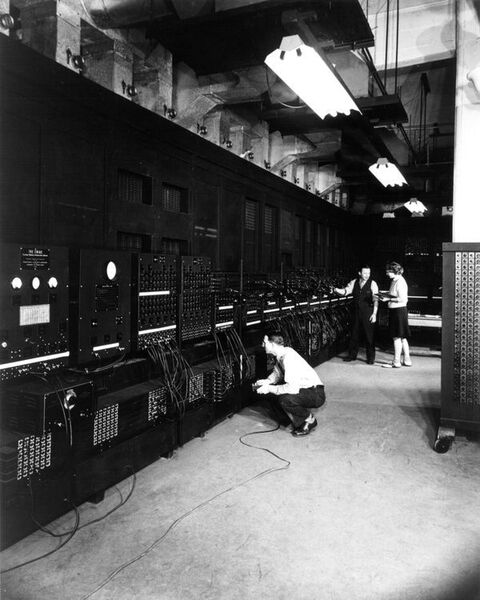

世界最初の電子式汎用コンピューター

ENIAC(エニアック)が誕生

前回の最後でENIACに触れた。世界最初の「電子式『汎用』コンピューター」である。つまり機械式リレーや歯車/モーターを使わない、純粋に真空管のみで構成されたシステムである。

画像の出典は、Comuter History Museum

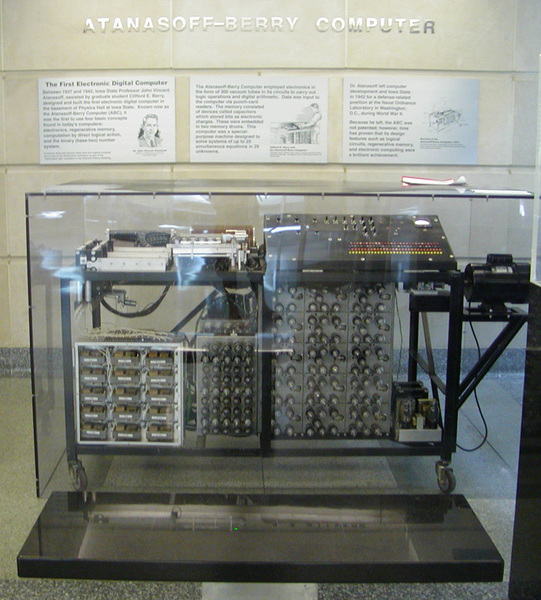

以前は「汎用」という文言が入らずに「世界最初の電子式コンピューター」と呼ばれていたのだが、ENIACに先んじてABC(Atanasoff-Berry Computer)と呼ばれる、やはり電子式のコンピューターが1942年に完成していた。

画像の出典は、Wikipedia

開発したのはアイオワ州立大学のJohn Vincent Atanasoff教授と教え子のClifford Berry氏で、彼らの名前を取った形だ。あいにくABCはプログラム内蔵式でないとか、目的は(Atanasoff教授の研究に必要な)最大29元の連立方程式を解くというもので、このあたりもあって「汎用」とは呼びにくい。

ただこのABCは1942年からさまざまな物理分野の計算や、同様の計算が必要だった同大農学部での計算に用いられた実績があるため、現在では世界最初の電子式コンピューターというとこのABCを指すのが一般的である。

アメリカ陸軍将校の目に留まったことから

ENIACの開発がスタート

話をENIACに戻す。ENIACはペンシルバニア大のムーアスクール(Moore School of Electrical Engineering:これは既に存在していない)のJohn Mauchly教授が、電子式コンピューターのプロポーザルを作ったところからスタートする。

Mauchly教授はムーアスクールでさまざまな電子式コンピューターを研究しており、このムーアスクールの卒業生だったJ. Presper Eckert氏が協力してプロポーザル(と、その後の設計)を手伝った。

Mauchly教授は自身のプロポーザルを備忘録の形でムーアスクール内で回覧している。この備忘録は、アメリカ陸軍からムーアスクールに来ていた連絡将校のHerman Goldstine中尉の目に留まった。

当時陸軍は、それこそ前回紹介した弾道計算以外にも多くの科学技術計算の必要性があり、これらを高速に処理できるコンピューターのシステムを模索していた。

かくしてGoldstine中尉はMauchly教授に正式なプロポーザルを出すように依頼し、これを基に1943年4月にアメリカ陸軍とムーアスクールの間で“Project PX”という名前での契約が結ばれ、ENIACの開発がスタートすることになった。

大学に連絡将校がいるのは、昨今の状況では違和感があるかもしれないが、この当時はそれほど珍しいものでもなかった。実際ムーアスクールでEckert氏はレーダータイミングの研究をしており、また1941年からはムーアスクールで行なわれていたESMWT(Engineering, Science, and Management War Training)という、アメリカの旧陸軍省がスポンサーの夏期講習で先生を手伝ったりしている。

軍事と大学は、この当時非常に近しい関係にあった時代だからこそ、という話でもある。そんなわけでProject PXがスタートしてMauchly教授は概念設計を、Eckert氏はハードウェアエンジニアリングの指揮をそれぞれとることになった。

ただ、Mauchly教授やEckert氏に加え、多くのムーアスクールの有能な人間やエンジニアが加わったとはいえ、あくまでも大学であるため製品の製造過程をすべて自身で行なうのは無理がある(これは陸軍も同じことだ)。

したがって製造にあたっては、多くの企業と契約を結び、共同で開発と製造をすることになる。そうした企業の中にはもちろんIBMも含まれていた。IBMはENIACの開発に際してペンシルバニア大と契約を結び、ハードウェアの製造などを提供している。

またENIACは入出力にIBMのパンチカードを利用しており、また打ち出されたパンチカードはIBMのTabulating machineを使って印刷できるようになっていた。このあたりの周辺機器に関してもIBMが手掛けたのではないかと思われる。

このENIACの開発は前回説明したSSECとは別の部隊が並行して行なっていたので、SSECの開発にはあまり関係がなかったのだが、ENIACの製造とその後の運用は、IBMにとって得難い経験を獲得するチャンスだったようだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ