GeForce RTXシリーズの

アーキテクチャーを大予想

さて、ここまでは前座でいよいよ本命のGeForce RTXシリーズである。実のところ、こちらもまだ詳細はわかっていない。意識してのことだとは思われるが、NVIDIAはまだTuringアーキテクチャーに関するホワイトペーパーなどを公開しておらず、なのでRT Coreの実装や、SM(Streaming Multiprocessor)がどういう構造になっているのかはさっぱりわからない。

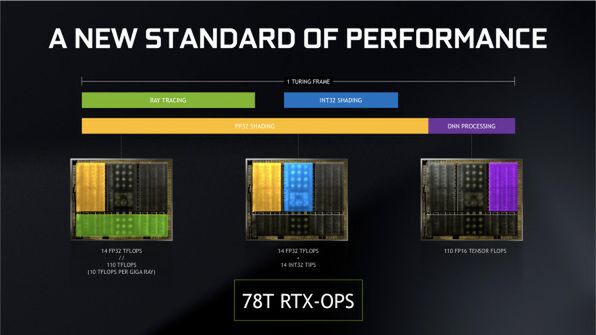

あるいはNVIDIAが新しく公開したRTX-OPSという指標も、なにをどうやるとこの78T RTX-OPSが算出されるのか不明なままである。

このあたりは今後製品が出荷されるころまでに明らかにされることを期待しつつ、とりあえずイッペイ氏の記事に示されたスペックを基にロードマップを描き直したのが下図である。

CUDAコア数こそ明らかになっているが、その他の話は今のところ未公開なので、これらは全部推定(なので数字には“?”がついている)である。この推定の根拠を説明しよう。

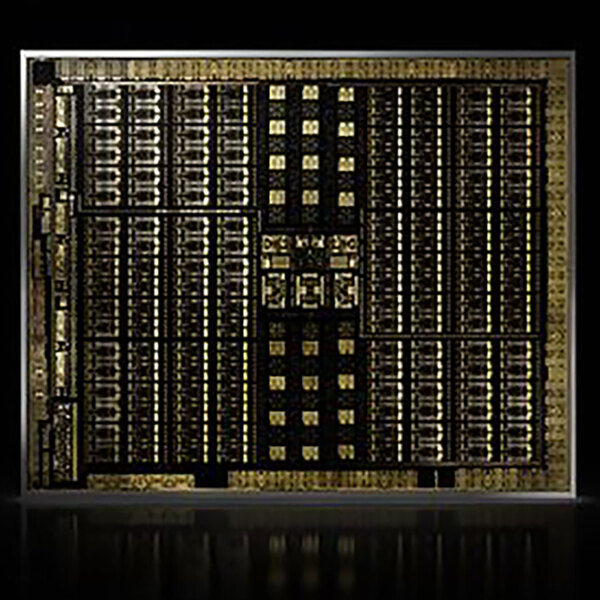

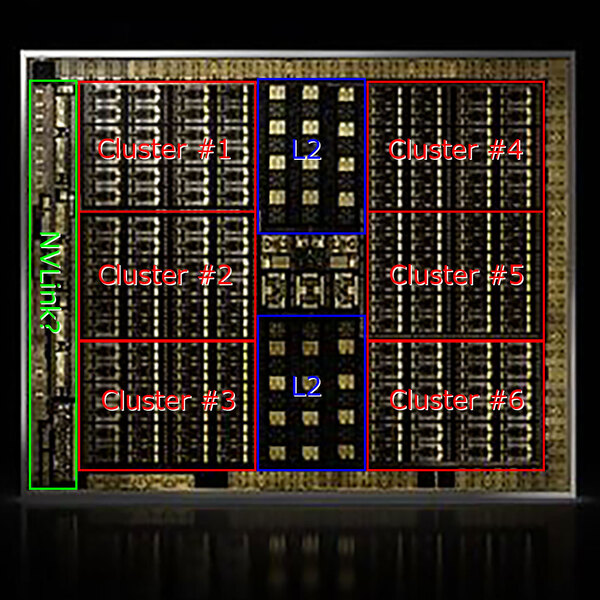

下の画像はNVIDIA提供の、TU102コアのダイ写真である。ちなみにTU102、というコード名も公式にはまだ明らかにされていない。今までだとGTになりそうだが、あいにくGTシリーズはすでに使われている。あるいはRTXシリーズでR、TuringでTということでRT102、なんて話も出ていたが、TU102というのが一番確度は高いらしい。

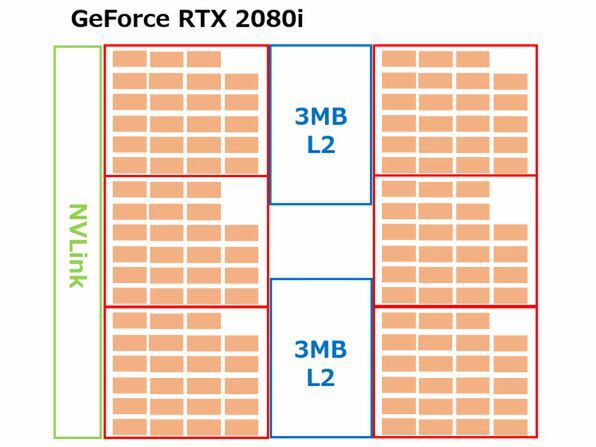

それはともかくこのTU102の内部ブロックを見ると、大きく6つのブロックがあり、それぞれの中に6行4列の演算ユニットがある。これを6行4列とみるか12行4列とみるかは難しいが、後述の理由により6行4列の方が辻褄が合いやすいので、6行4列案を取る。

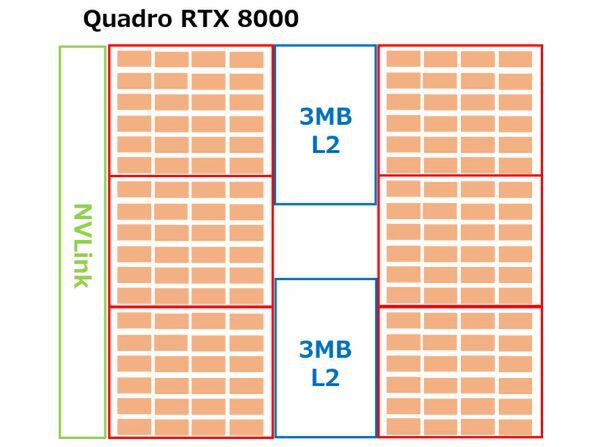

TU102コア(Quadro RTX 8000)は6つのクラスターがあり、それぞれのクラスターが24個のSMを持ち、各々のSMが32演算(Intの場合)を同時に処理すると考えると、CUDAコア総数は6×24×32=4608となり、Quadro RTX 8000の4608 CUDAコアというスペックに合致することになる。

問題はGeForce RTXである。GeForce RTX 2080 Tiの場合、コアそのものは間違いなくTU102のままであると思われる。ただしCUDAコアが4352という、謎な数字になっているが、これを6クラスター/32演算で割ると、1クラスターあたり22.6667……SMになる。ただこれも実際には簡単で、1クラスターあたり23SMコアにしつつ、うち2クラスターのみ22SMにすれば、6クラスター合計で136SM、4352CUDAコアになる。

ちなみにテクスチャーユニットはPascal世代の製品構成を睨みつつ、一応クラスターあたり48ユニットと仮定してみた。一方ROPについては、メモリーコントローラ(32bit)あたり10ユニットと仮定している。

この結果、GeForce RTX 2080Tiは6クラスターなのでテクスチャーユニットは288ユニット、一方ROPユニットは352bit Bus(32bit×11ch)でメモリーチャネルが11個なので、110ユニットとしている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ