10nmプロセスの問題点は

配線の微細化

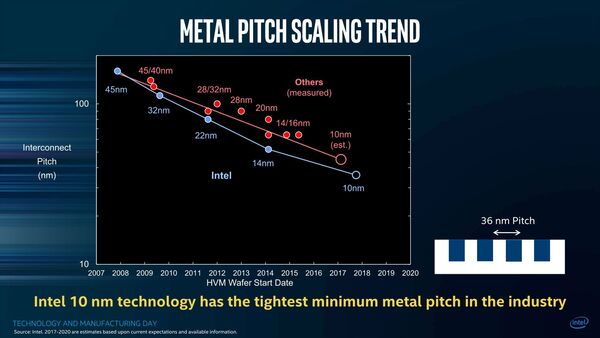

昨今なぜ配線層が急に問題になってきたかというと、配線の微細化が進んだからだ。連載419回のMetal Pitchをご覧いただくとわかるが、32nm世代では配線の間隔は100nm程度であった。これが10nm世代では36nmまで狭まっている。

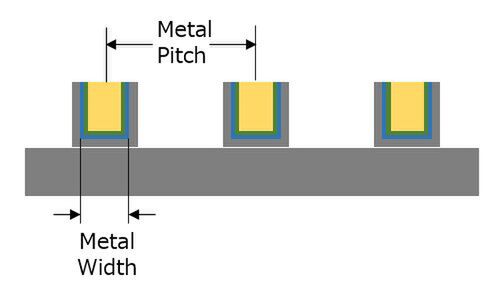

ちなみにこの100nmや36nmというのは配線の幅そのものではなく、配線同士の間隔であって、配線そのものの幅はインテルは公表していない。

ただラフに言えばほぼMetal Pitchの半分なので、100nm世代なら50nmほど、36nmということは18nmという計算になる。ただ、50nmなり18nmがまるごと全部配線ではない。

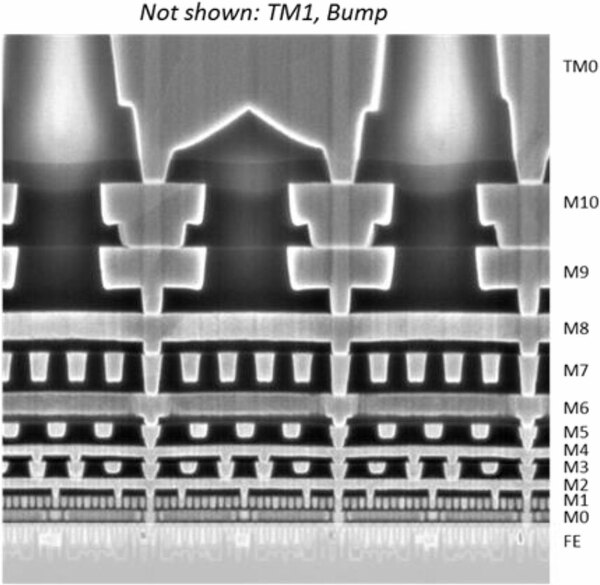

画像の出典は、IEDM 2017におけるIntelの“A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact over Active Gate and Cobalt Local Interconnects”という論文。

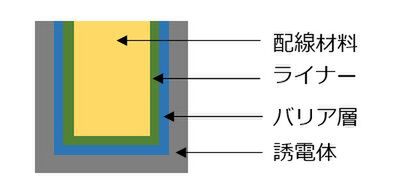

下図がその配線部の中身だが、誘電体は考える必要がないのでおいておくと、まず外側にバリア層がある。これは銅配線の際に導入されたものである。銅は抵抗が低い代わりに、他の材料を汚染するという厄介な性質があり、この銅イオンが外部に逃げ出さないように封をするのがバリア層である。

これが数nmほどの厚みがある。次がライナー層で、配線材料(銅)とバリア層をくっつける、いわば接着剤の様な機能を持つものだが、こちらも数nmの厚みがある。仮にバリア層とライナーがどちらも1nmの厚みだとすると、50nmの場合銅配線の実質的な幅は46nmであるが、18nmの場合は14nmまで減ることになる。配線を微細化といっても、バリア層やライナーの厚みはそうそう変えられないからだ。

エレクトロマイグレーションの発生には、配線材料の電子の平均自由行程と呼ばれるものが関係してくる。これもラフに言えば、配線幅が平均自由行程を下回るほど狭くなると、急激に衝突が発生することになる。銅配線の中での電子の平均自由行程は40nmほどであり、32nm世代の46nm幅ならそれほど問題はないが、10nm世代の14nm幅ではかなり厳しい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ