今週からしばらくは中休みということで、用語集をお届けする。「なぜ用語集?」というと、ジサトラメンバーから「用語は知ってるけれど、ちゃんと理解してない」言葉がいくつかある、という話が出てきていたので「それじゃ中休みがてら説明しましょう」ということである。そんなわけで単語の選定は、主にジサトラメンバーからあがってきたものである。その一発目はRing Busである。

そもそもバスって何よ? という話は以前連載105回や218回で簡単に触れたが、要するにPCの内部のコンポーネント同士をつなぐのがバスである。

CPUとメモリーをつながないと、CPUが処理をするためのデータが永遠に手に入らない。メモリーとGPUをつながないと、いくら待っても画面は真っ暗なままである。そんなわけで、バスもまたPCの内部では非常に重要(ただし陽があたらない、影の存在)である。

さて、以前の連載では規格別にバスを紹介したが、少し別の観点からバスを分類してみる。トポロジー(つまりつなぎ方)で言うと、バスには以下の3種類がある。

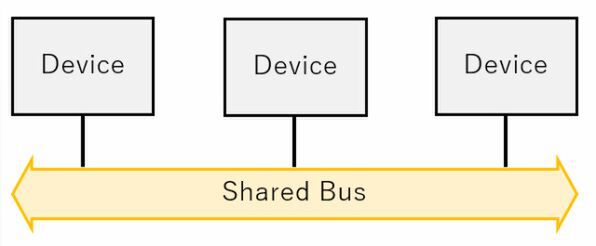

(1) 共有バス

複数のデバイスが1本のバスを共有する形だ。この方式は以下の特徴がある。

| 共有バスの仕組み | ||||||

|---|---|---|---|---|---|---|

| メリット | 構造がシンプルで、デバイスの数を簡単に増やしやすい。 1つのデバイスからほかのデバイスに一斉にデータを送れる(Broadcast)。 バスのデータ幅を増やしても、実装面積が最小に抑えられる。 |

|||||

| デメリット | あるDeviceの送信中は、ほかのデバイスが送信できない。 信号が高速になると、波形が乱れやすい(特にデバイス数が増えると顕著)。 デバイス間の調停機構(誰がいつまでの間送信できるか、を決める)が必要。 |

|||||

この共有バスは、かつてはインテルのFSB(Front Side Bus)で利用されており、ほかにもISA/PCIやLPC、Enhanced IDEなど非常に幅広く使われていた。現在もメインメモリーや、周辺回路でもI2Cなどは引き続き共有バス形式である。また広義に言えば、Wi-FiやBluetoothなど無線を利用したネットワークは、分類としては共有バスということになる。

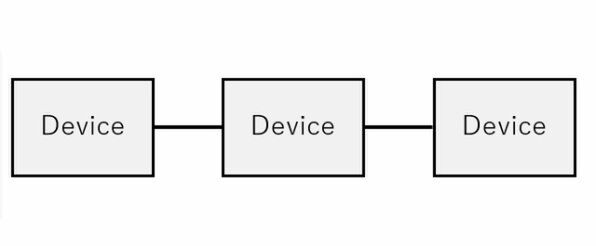

(2) Point-to-Point

個々のデバイスが一対一接続する形だ。この方式の場合以下の特徴がある。

| Point-to-Pointの仕組み | ||||||

|---|---|---|---|---|---|---|

| メリット | 速度やバスのデータ幅を自由に選べるし、特に速度を非常に上げやすい。 小規模な構成であれば、最小の面積で実装できる。 |

|||||

| デメリット | デバイスの個数が増えると、途端に配線の数が爆発的に増えることになる。 ある程度以上の構成ではハブをはさむ形にすることが多いが、大規模になるとハブを複数個つなげることになり、これのレイテンシーや消費電力がバカにならない。 大規模なハブは、内部が複雑化する。 |

|||||

Point-to-Pointが現在の主流であって、Nehalem以降のCPUの接続やPCI Express、Serial ATA、GDDR、USB、Thunderbolt、HDMI、DisplayPortなどさまざまなI/Fがこの構造を取っている。ネットワークでも、10BASE-T以降のすべてのイーサネットはこの方式である。

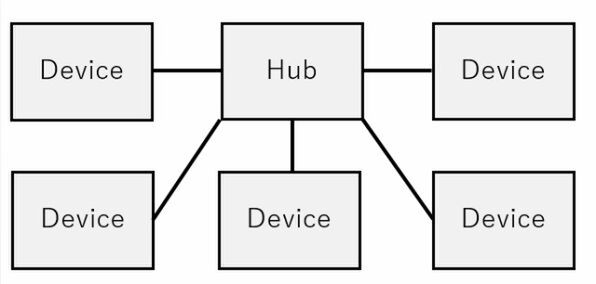

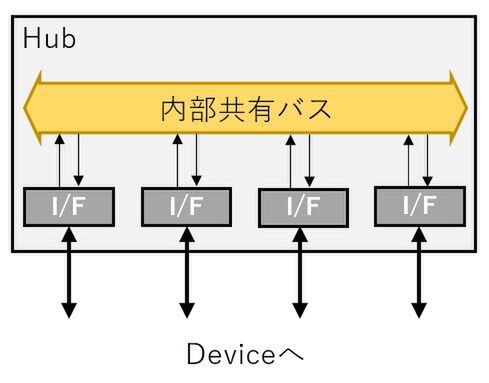

ちなみにこのハブの内部構造はこれも2種類あり、大別すると共有バス方式のものと、Switch(Fabricという言い方をする場合もある)方式である。下図が共有バス方式のもので、昔のUSB 1.1/2.0のハブなどはこうした実装であった。

この方式ではコストが安く済む一方、共有バス方式のデメリットを全部引き継ぐことになってしまうため、最近はあまり使われていない。

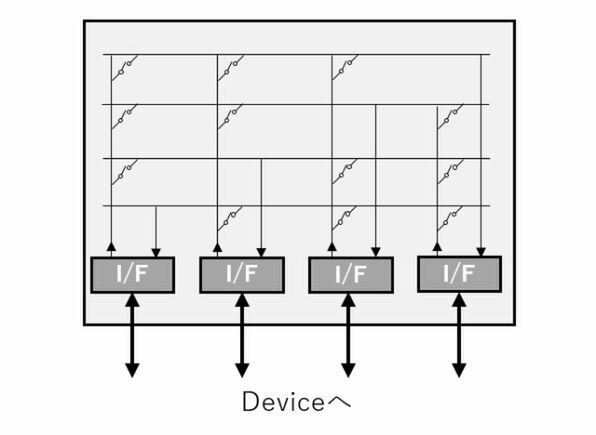

一方のSwitchは、最小構成では下の構図になっている。それぞれのデバイス用のI/Fから、縦横構造の配線に信号が渡されて、目的のデバイスにつながる形だ。

この方式、昔は電話交換機に使われており、縦方向の信号線に横方向のショートカット(横木)を当てる形なのでCrossbar、と呼ばれていた。最近では縦横の配線がまるで織物のようだ、ということでFabricと呼ばれることもあるが、Switch/Crossbar/Fabricのいずれも同じものを指している。

このSwitchは、たとえばDevice AとBが通信しながら、同時にDevice CとDが通信することもできるといったメリットがあり、レイテンシーも共有バス方式よりもずっと少ない反面、つながるデバイス(この図で言えば縦方向の配線)の数の2乗のサイズで回路規模が大きくなる、という欠点がある。

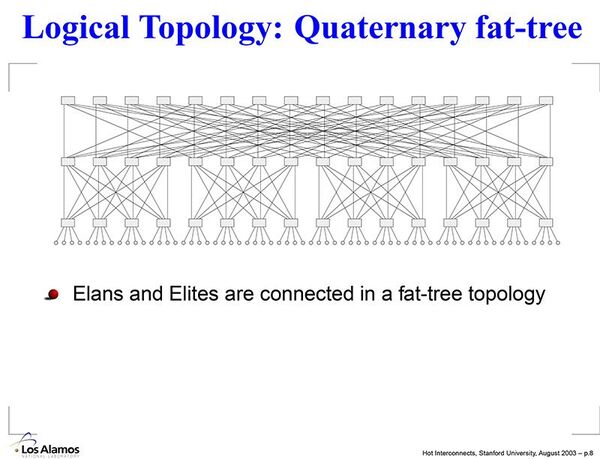

したがって大規模なSwitchは高コストになるという欠点もある。そこで複数個のスイッチをツリー状につなげる、という使われ方をする場合もある。スーパーコンピューターのASCI QがElite(これがSwitch)を3層のFat Treeにしたというのも、1個で3000台をブラ下げられるSwitchを作ることが技術的に不可能だからこその対策である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ