業界に痕跡を残して消えたメーカーで、C&T、OPTiと古いチップセットメーカーを紹介したところで、続いてはもう少し新しいメーカーであるReliance Computer Corp.(RCC)を取り上げたい。

「そんなメーカーあったっけ?」という方も、ServerWorks Corp.という名前には聞き覚えがあるかもしれない。実は両社は同一というか、まずRCCという名前で創業され、その後新規株式公開をした段階で社名をServerWorksに変更している。

おまけに製品名を社名変更のついでに変更してくれたおかげで、両方が混じって表記されている記事もあったりして、わかりにくいことこのうえない。一応この記事では時系列にそって、その時点における社名/製品名を表記するつもりだ。

x86のサーバー向けチップセットに

商機を見出し創業

RCCはRaju Vegesna氏によって1994年に創業された。会社はカリフォルニア州サンタクララで、インテルの本社からそう遠くない場所だ。ちなみに現在はBroadcomがそこに入居している。

Vegesna氏は元々MotorolaでMC68030のマイクロコード開発やMC68040の仕様策定に携わっており、その後ROSS Technology Inc.の創業に携わり、ここで設計開発長としてHyperSPARCの開発に携わっている。

本来はCPU屋さんだったはずのVegesna氏だが、RCCではあえてチップセットを商品とすることにした。ただしRCCが狙ったのはデスクトップやノートではなく、x86のサーバー向けである。

1994年というのは、そろそろPentium Proの話がちらちら業界に出てきた頃である。当時はまだx86はPentiumの2P構成がある程度で、本格的なサーバーには適さないと考えられていたが、Pentium ProはCPU単体での性能も高く、かつマルチCPU構成に向いた製品とみなされていた。

ただしチップセットの方はお世辞にも十分とはいえなかった。以前黒歴史でMercedを取り上げた時にも触れたが、インテルが高速な広帯域バスに習熟したのはそれこそDirect RDRAMのお陰……とまで言うと言い過ぎかも知れないが、2000年代後半に入ってからの話で、当時はまだマルチドロップのFSBを高速に動作させるのに十分な技術を持っているとは言えなかった。Vegasna氏はここに商機を見出したようだ。

最初の製品は1996年頃に投入された、Champion 1.0である。これは後にServerSet Iと呼ばれるようになっている。Champion 1.0の情報は少ないのだが、製造そのものはNECで行なわれている。対応するのはPentium Proで、2P構成のLEと4P以上の構成が可能なHEがあったと思われる。

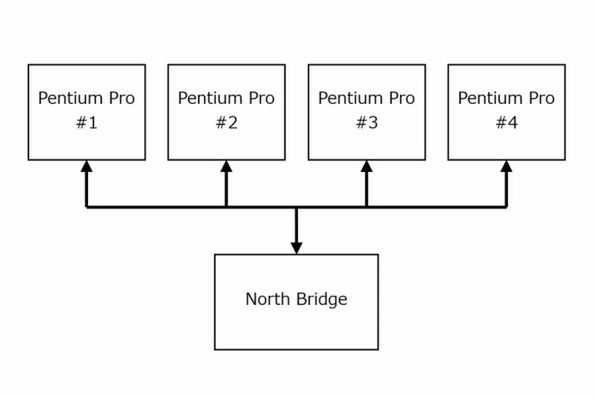

Pentium Proそのものは4Pまでしか考慮しておらず、4P以上を構成するためには細工が必要になる。ではHEではどんな細工を施したかという話である。下図は通常の4P構成で、これはインテルの450GXと同じものだ。

これを超える6Pについては、下図のようにCPUを2つづつ3つのグループに分け、それぞれにFSBブリッジのようなバッファを挟み込む。

このケースで、例えばCPU #1からは、同じFSBの上にCPU #2とFSB Bridge #1/#2という3つのプロセッサーがいるように見える。要するにFSBブリッジが2つのCPUのキャッシュスヌーピングや割り込みなどの信号を、仮想的に1つのCPUからのものにまとめて見せてくれるという仕組みだ。

この仕組みを応用すると8P構成も可能になる。下図がそれで、FSBブリッジを2段に挟み込む形だ。この場合、CPU #1からCPU #2はそのまま、CPU #3・#4はFSB Bridge #2として、CPU #5~#8はFSB Bridge #6として見えることになり、4つしかCPUが見えないにも関わらず8Pが可能になるというマジックである。

NECはこのChampion 1.0を搭載して最大8P(6P構成も可能と当時NECの方にお聞きした記憶がある)構成が取れるExpress5800/190Proを1996年10月に発表している。

実はこの構成、確かにCPUの数は増やせるが、最終的にノースブリッジとつながるFSBは1本しかないのが問題で、ここがボトルネックになりがちという根本的な問題は解決しないのだが、1990年代後半は、まだそこまで大量のデータの処理は要求されていなかったから、これでも間に合ったと思われる。

また先のExpress5800/190Proの仕様を見ると、8P構成では16MB L3キャッシュ×2が搭載される。これがChampion 1.0に標準の機能なのか、NEC向けの独自拡張なのかは判断できないが、構造的にはFSB Bridge #5/#6に外付けの形でキャッシュを利用できたようだ。

確かにこの位置にキャッシュを持てれば、FSBの帯域が足りない問題にある程度の解決策となるだろう。

余談であるが、同様にChampion 1.0を搭載したと思われる三菱電機のapricot FT8000シリーズのモデル800は、Pentium Pro 200MHz×8の構成に「4MBのシステムキャッシュ」を搭載しているとする。

上図の構成で、FSB Bridge #5/#6にそれぞれ2MBのL3キャッシュを持っていたように読める。またNECは、1998年11月には、L3キャッシュを32MB×2に増強したExpress5800/190DProをリリースしており、キャッシュ容量にはかなり柔軟性があったようにも思えるが、この頃同社はセミカスタムに近い形で各メーカーの仕様にあわせたチップセットをリリースしているので、これがChampion 1.0の標準的な仕様かどうかは断言できない。

Champion 1.0はまだRCCがベンチャーということもあり、幅広い採用というには至らなかった。当時はまだx86のサーバー市場そのものが小さかったという問題もある。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ