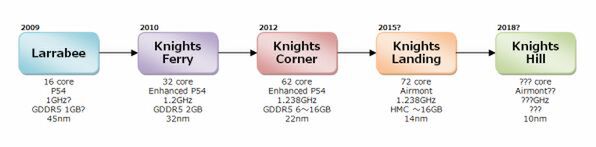

前回のスーパーコンピューターの系譜は、インテルのKnights Cornerの話で終わってしまったので、今回はこれに続く2製品、それと連載314回の最後で説明した、「欠けている要素」に関する話をしていきたい。

Silvermontベースの

Knights Landing

2014年6月に開催されたISC14で、インテルはKnights Landingという新しいMIC(Many Integrated Core)アーキテクチャーの説明を行なった。

この時点で公開された情報は以下の3つで、これが骨子となっている。

- CPUコアそのものが、従来のP54ベースのものからSilvermont(14nmを使うので事実上はAirmont)ベースのものに切り替わる。この結果、シングルスレッドでの性能が従来比で3倍となった

- パッケージ単体で理論性能3TFLOPS(倍精度)が実現できるようになる

- 3D積層メモリーをオンパッケージで搭載し、最大16GBの容量とDDR4比で5倍の帯域を確保できるようになる

まず1つ目。P54は回路規模が小さく、比較的簡単に使えるということでインテル社内、特に研究開発チームで使いまわされているそうで、インテルのQuark X1000コアがP54ベースなのもこのあたりに理由があったらしい。

しかし、いかんせん2命令のIn-Orderスーパースカラーといいつつも、実態は同じ2命令/サイクルのIn-OrderスーパースカラーのAtomコアと同じ程度の性能で、ベクトル演算はともかくそれ以外の処理が遅いという問題を抱えていたままだった。

実はP54と初代Atomコア(Silverthorne)の性能比較に関する公式な数字がないのだが、こういう便利な数字を示してくださるサイトがあり、PentiumとAtomの性能を比較すると以下のようになる。

| PentiumとAtomの性能比較 | ||||||

|---|---|---|---|---|---|---|

| Freq (MHz) |

Dhry1 Opt |

Dhry1 NoOpt |

Dhry2 Opt |

Dhry2 NoOpt |

||

| P54 | 100 | 169 | 31.8 | 122 | 32.2 | |

| Atom | 1600 | 2462 | 717 | 1828 | 728 | |

これから、性能/動作周波数比を求めると下表のようになる。

| PentiumとAtomの性能/動作周波数比 | ||||||

|---|---|---|---|---|---|---|

| Dhry1 Opt |

Dhry1 NoOpt |

Dhry2 Opt |

Dhry2 NoOpt |

|||

| P54 | 1.69 | 0.32 | 1.22 | 0.32 | ||

| Atom | 1.54 | 0.45 | 1.14 | 0.46 | ||

浮動小数点演算を含まないベンチマークのDhrystoneでいいのか? という疑問はともかく、最適化するとPentiumの方が速いが最適化なしだとAtomの方が高速で、ただどちらも似たようなレベルで、そう性能に差がないことがわかる。

なるほど、Knights CornerがP54をSilverthorneに入れ替えなかった理由が理解できる。個人的には、P54コアを無理やり64bit対応にする手間をかけるくらいなら、Silverthorneコアに入れ替えた方が早かった気がするのだが、このあたりの事情はよくわらない。

この結果として3倍の性能が得られたとするのだが、これが整数演算性能なのか、浮動小数点演算性能なのかは明示されていない。

ただ「Xeon Phi 5110P」は倍精度でおおむね1.01TFLOPSとされ、一方Knights Landingは倍精度で3TFLOPS以上としているため、この3倍は浮動小数点演算の方で、整数演算性能はそこまで伸びていないだろうと思われる。

メモリーは「インテルとMicron Technologyの共同開発」と書かれていることから、いわゆるHMC(Hybrid Memory Cube)、もしくはその派生型を採用していると考えられる。

→次のページヘ続く (単体でOSが動作するのが最大の特徴)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ