ワンチップに複数コアを組み込む作戦で

Larrabeeを活用

結局インテルはGPUの代替としてLarrabeeを利用することを放棄、既存のIntel GMAアーキテクチャーを引き続き改良し続けることにした。これは妥当というか、適切な戦略であったと思う。ただそれはそれとして、Larrabeeのアーキテクチャーそのものはまだ利用できる、とインテル自身は考えていた。それはまさしくHPC向けの用途である。

もともとインテルはMPP(Massive Parallel Processing:超並列)に広く精通していた。その最初のものはiPSCで、これにParagonが続き、ASCI Redにつながることになる。

これらのシステムは、いずれも汎用のx86プロセッサーを密結合する形でシステムを構築しており、当然その分システムのサイズや消費電力は大きくなっている。ところが、Larrabeeのようにワンチップの中に複数のx86コアが統合される構成なら、1個1個の性能は多少低くても、トータルとしての性能/消費電力比を高めることで、結果的に高性能なシステムを構築可能になる。

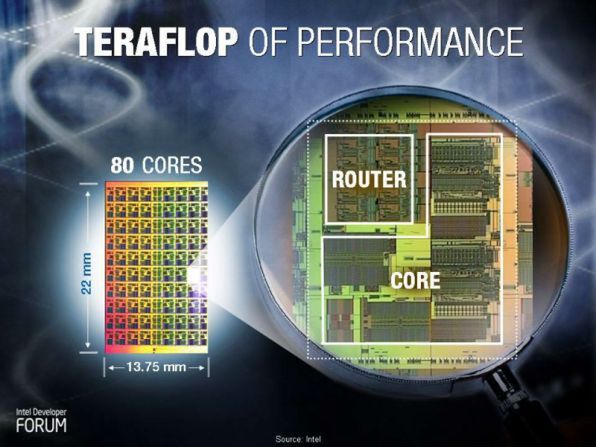

ASCI Redを最後に、大規模なHPC向けシステムをインテルは開発・納入していないが、研究開発チームは継続してこうした研究を続けてきた。その一例が2006年のIDFで発表された80コアのチップである。このコアはx86とは互換性のない独自のものだが、TFLOPSクラスの性能と、3.1GHz動作の場合で10GFLOPS/Wの性能を実現できることを発表している。

ISSCC 2007ではもうすこし突っ込んだ説明があり、1GHz動作で0.32TFLOPS、3.1GHzで1TFLOPS、ピークは5.67GHz駆動で1.8TFLOPSの性能になることが明らかにされている。これはあくまでも試作であって、同じ仕組みがLarrabeeに適用できるわけではないが、ワンチップに複数コアを組み込むMany Coreの方向性とLarrabeeは相性が良い、と判断したようだ。

この結果インテルはLarrabeeの方向性を大きく変更し、HPCに向けたMany Coreのプラットフォームとして活用することにする。とは言え、この時点では大きく2つの要素が欠けていた。1つは絶対性能で、なにしろ16コアしかないため、いくら16wayのSIMDエンジンでもピーク性能はそう高くないし、実効性能はさらに見劣りする。

もう1つは適切なプログラミング環境である。NVIDIAのCUDA、あるいはAMDのBrook+に相当するものを、この時点でインテルはLarrabee向けに提供できていなかった。そこでここから猛然とインテルは欠けているパーツを埋めるべく奔走し始める。続きは次回説明しよう。

この連載の記事

-

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 - この連載の一覧へ