「バンク」によって大容量化と

高速化を実現した72pin SIMM

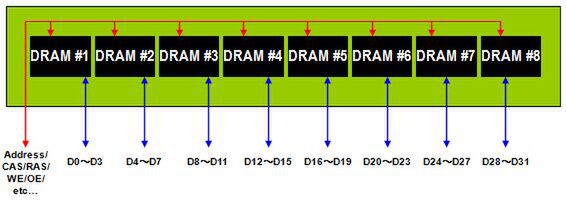

「72pin SIMM」のおおまかな構造は図2のようになる。アドレス線や各種信号線は共用で、データ線をDRAMチップごとに分割するというスタイルは30pin SIMMと同じだ。データ幅が32bit分になったのが大きな違いとなる。これによって、メモリー増設の際にはSIMMを1枚単位で増設できることになった。

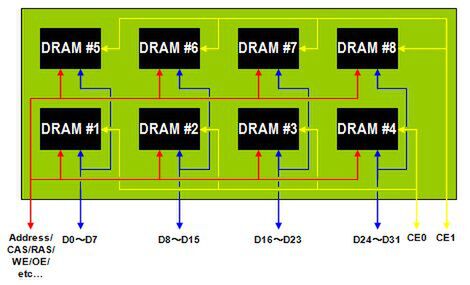

72pin SIMMでは「バンク」という概念も追加された。正確に言えば、16bit幅の60pin SIMMですでにバンクの仕様が追加されており、72pinでもこれを引き継いだわけだ。図3は8bit幅のDRAMチップを使った場合の、2バンク仕様のSIMMの構造である。

本来8bit幅のDRAMチップなら、4つで32bit幅を構成できる。だが、4つではメモリー容量が要求に満たない場合があり、実装するDRAMチップの数を増やす必要がある。この際に、「CE0」(Chip Enable 0)と「CE1」という2本の信号線を使って対象となるDRAMを選択することで、D0~D31の32bit分のデータ線を共用することが可能になった。

このバンク切り替えは、のちに「バンクインターリーブ」という高速化手法でも利用されることになった。初めにDRAM #1~#4と#5~#8へ同時にリクエストを出しておく。そしてまずはCE0をセットしてDRAM #1~#4から出力し、ついでCE1をセットしてDRAM #5~#8を出力させるという方法だ。これにより、DRAM #1~DRAM #8までのトータルのアクセス時間をやや高速化できる。

この72pin SIMMが普及した時期でも、ほかに64pin SIMMや88pin SIMM、112pin SO-DIMMや100pin DIMMといった、いくつかの異なる規格があった。64pin SIMMは「Macintosh II fx」などでも採用されたが、結局は広く普及することなく終わっている。

64bitバスに対応する「DIMM」が登場

72pin SIMMに続いて登場したのが「DIMM」(Dual In-line Memory Module)である。SIMMとDIMMの最大の違いは、「信号ピンが片側か両側か」だ。実は一部のSIMMには、基板の表裏の両方に信号ピンが用意されていた。しかし、電気的には表と裏はつながっていたので、実際は1列分しか信号ピンがないのと同じだった。

一方、DIMMでは基板の表と裏で、別々の信号ピンが割り当てられている。結果として、72pin SIMMと最初に登場したDIMMでは寸法はそれほど変わらなかったのに、ピン数は168pinまで増えている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ