インテル(株)は17日、東京・秋葉原にて「インテル プラットフォーム技術セミナー 2007」を開催。「環境」をテーマに、電力効率の高いCPUやプラットフォーム技術や、データセンター開発、ITに関する環境調和型社会の実現への取り組みなどについての講演が行なわれた。

基調講演では、米インテル社 マイクロプロセッサー・テクノロジー・ラボ ディレクターのシェーカー・ボーカー(Shekhar Borkar)氏(コーポレート・テクノロジー統括本部 インテル・フェロー)により、高性能で低消費電力なマルチコアCPUの方向性と、試作80コア・TFLOPSチップのアーキテクチャーについての説明が行なわれた。

基調講演の前に挨拶に立ったインテル 代表取締役共同社長の吉田和正氏は、同社もまたさまざまな形で、地球温暖化対策を主とした環境問題に対して貢献を行なうと述べた。吉田氏は環境問題に配慮した「グリーンIT」への取り組みは時代の要請であるとし、、インテルと米グーグル社などが主導した業界団体「Climate Savers Computing Initiative」や、日本の経済産業省主導で行なわれている「グリーンITプロジェクト」など、IT業界全体での取り組みを挙げた。

また、インテル自身による取り組みについては、自社の製造現場での改善と、技術面での改善の2つを挙げた。まず前者については、工場での水や電力使用量の削減、プロセッサーの鉛フリー化実現とハロゲンフリー化の推進などを行なっているという。後者を吉田氏は、同社にとってのメインテーマと位置づけ、アーキテクチャーの改良と製造プロセスの微細化などを通じて、電力効率に優れたプロセッサーの性能向上を推進することで、温暖化ガス排出量の抑制に役立つとしている。ボーカー氏の講演で語られたのも、後者に基づく取り組みの例である。

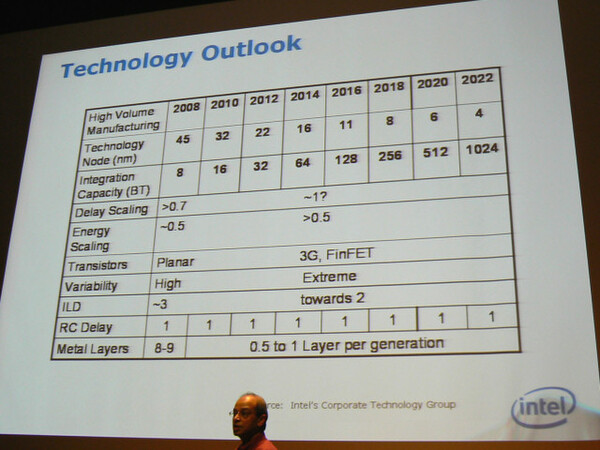

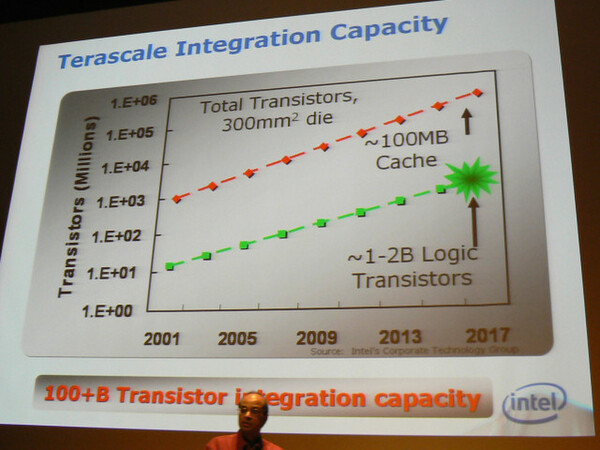

ボーカー氏の講演内容を大雑把にまとめると、「プロセス微細化により増えるトランジスターを活用して、電力効率の優れたプロセッサーを作る」という点に集約される。ボーカー氏はまず、インテルの半導体製造プロセスの微細化ロードマップを示し、プロセス微細化と1チップに搭載可能なトランジスター数は今後も増大するとした。一方で、微細化による性能向上自体が難しくなりつつあるとの見方を示し、動作クロック周波数の向上や動作電圧の低減が困難になっていることを、いくつかのグラフを提示して解説した。

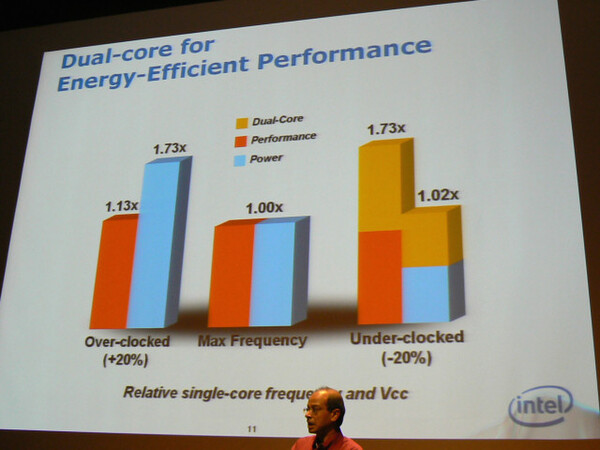

消費電力を抑えながら、トランジスター数の増加を性能向上に反映させる手段として、インテルや競合他社が推進しているのがCPUのマルチコア化だ。ボーカー氏は「シングルコアでは消費電力が倍になっても性能は40%程度しか向上しない。しかしマルチコアならリニアな向上が可能になる」と述べ、マルチコア化が今後の性能向上の有力な手段であるとした。ここまではよく耳にする話だ。

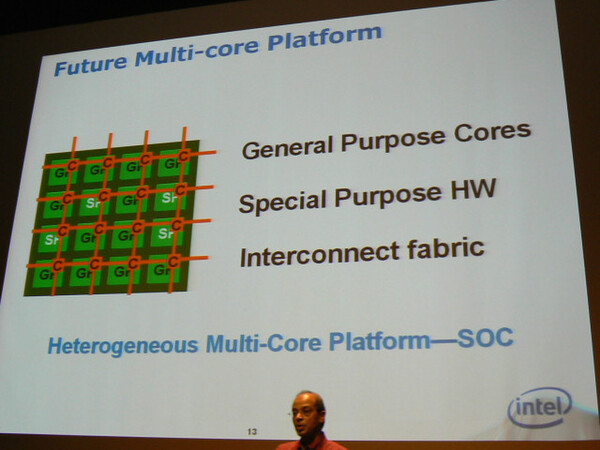

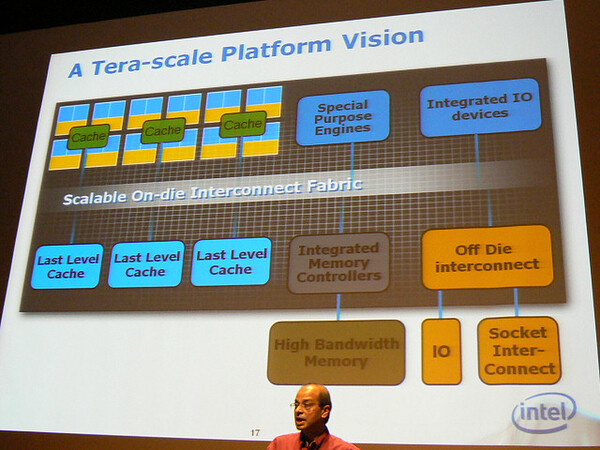

現在のデュアル~マルチコアCPUは、いずれも同じ機能を持つCPUコアを1パッケージ内に集積したCPUだ。しかし、ボーカー氏が将来のマルチコアCPUとして例示したのは、汎用的なCPUコアと特定機能に特化したコアをそれぞれ複数集積した“非対称型”のマルチコアCPUであった。1枚のCPUダイ上に、どちらも小さい汎用コア(GP)と特化型コア(SP)が複数集積され、それぞれをチップ間インターコネクトで接続する形態を想定している。

しかしボーカー氏はこの手法について、コアが小さくてもチップ内ネットワークの消費電力は大きいとの問題点もあると指摘。スループット、シングルスレッドプログラムの実行性能、コアとネットワークの消費電力といった3点を、慎重にバランスを取ることが重要であると述べた。

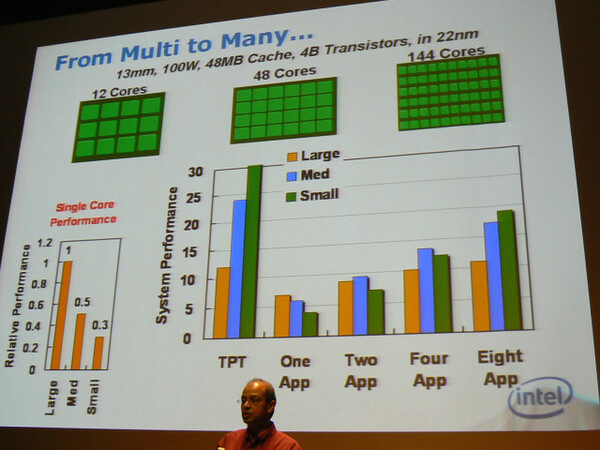

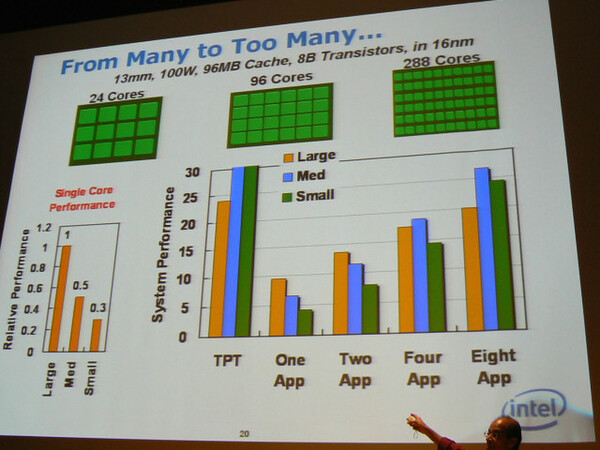

また、適切なコア数や設計についての例を示した。「製造プロセス22nmで、13mm平方、消費電力100W、48MBキャッシュ、40億個のトランジスター」のプロセッサーと、「同じサイズで製造プロセス16nm、消費電力100W、96MBキャッシュ、80億個のトランジスター」のプロセッサーを想定。それぞれ大型(前者は12コア、後者はその倍、以下同)・中型(48コア)・小型のコア(144コア)を多数搭載して複数のアプリケーションを同時実行した場合のパフォーマンスの変化をシミュレーションした結果を元に説明した。

前者の場合では、大型コア12個と中型コア48個の性能上のしきい値が2アプリケーション同時にあったのに対して、後者の場合は大型24個と中型96個のしきい値が4アプリケーション同時に状況になるという。

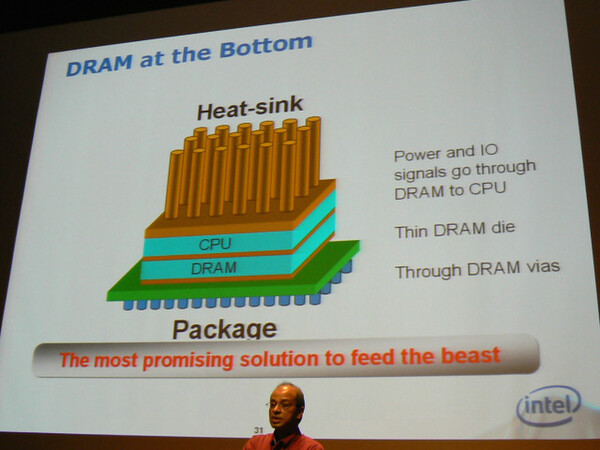

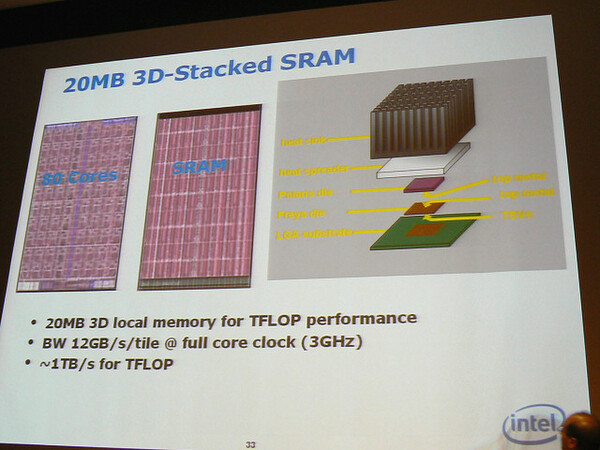

消費電力抑制のためのプロセッサー設計の分野では、“いかにしてダイ内部のチップ間配線距離を縮めるか”や“CPUとメモリーを1チップに混在する場合の設計例”が解説された。インテル製クアッドコアCPUのように、現在のマルチチップパッケージは、平面上に各チップを並べて相互に接続する形態を取っているが、ボーカー氏はこれを「十分ではない。中間的なもの」と表した。そして、CPUの上にDRAMチップを載せたパッケージと、DRAMチップ上にCPUを載せたパッケージの例を挙げて、DRAMチップに穴を開けて上に載せたCPUと下部のピンを結ぶ構成の方が、CPUとヒートシンクの距離が縮まって現実的であるとのことだ。

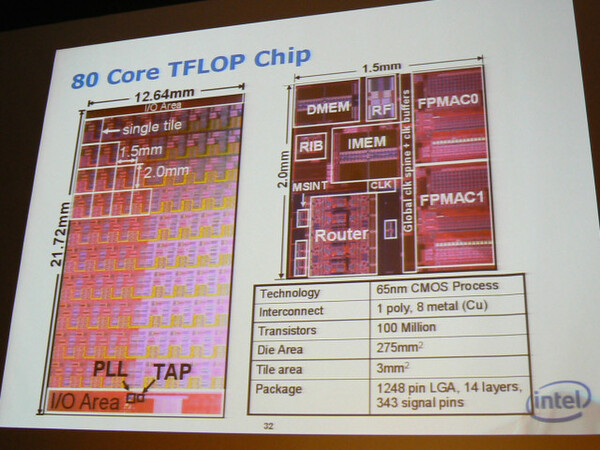

この手法で作られた、80コアのCPUと20MBのSRAMを積み重ねた試作チップの写真なども公開された。1.3Vで2TFLOPSもの性能を発揮できる「世界第1級のエネルギー効率」を持つなど、インテルが技術開発上の目標として掲げる「テラスケールコンピューティング」の実現に向けた取り組みが、着実に進展していることがうかがえる講演であった。