電力ロスを最小化!

チップの裏から給電するVPD(垂直給電)の仕組みと課題

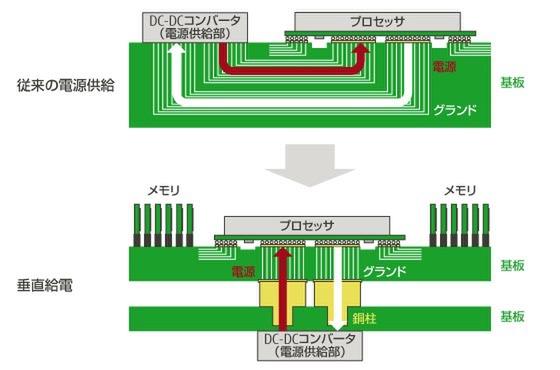

では電力配線はどうなっているか? が下の画像だ。これは従来型の、つまりチップの横にVR(Voltage Regulator)を配し、そこから基板内部の電源層経由でチップに供給を行う方式の模式図である。

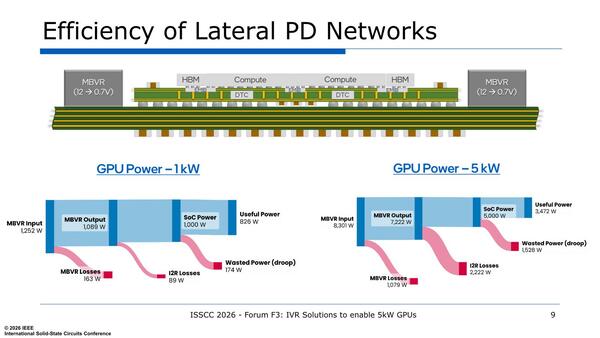

MBVRはMother Board VRの略で、続くIVR(Integrated VR)との対比のためにこう書いたのだろうが、あまり一般的な略ではない。Discrete VRにすればよかったのでは……

ここでGPUに1KWを供給するには1252Wの供給が必要であり、さらにGPU内部の電圧降下にともなうロスまで含めると、426Wが無駄になる。ところがこれが5KWになるとどうか? というとさらにひどく、MBVRのロスとI2Rロスで3301Wが無駄になり、内部で1528Wのロスが出る。トータルでは4829Wものロスで、入力された8301Wの半分以上が無駄に捨てられてしまう計算になる。

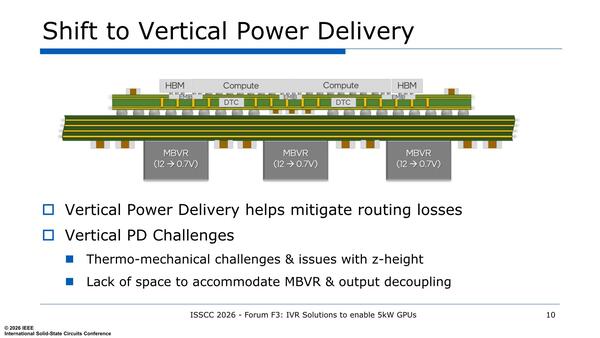

ちなみにI2Rロスというのは配線抵抗にともなう無駄な消費電力のことだ。1kWではそれほど大きくならないが、5kWではI2Rロスが一番大きい。MBVRのロスやチップ内部のロスはそれぞれ個別の対策が必要でパッケージ側ではなにもできないのだが、唯一I2Rロスを削減できる方法として今後導入されるのが確実視されているのがVPD(Vertical Power Delivery)である。

見ての通り、チップの真裏にVRを設置して、そこから基板を垂直に貫通する形で電力を供給することで、電力配線経路を最小限にしてロスを減らそう、という仕組みだ。

実はこの方式、すでに商用での実例がある。富士通が2017年に発表したSPARC M12がそれで、搭載されているプロセッサー(SPARC64 XII)の実装にあたって、VPD(Vertical Power Delivery)方式が採用されたことが富士通により明らかにされている。

もっともこの方式、現実で採用されている事例は非常に少ない。温度・機械的な要因(熱による歪みなど)と基板裏側にそれなりの高さの部品が配されること、それとパスコンを配する場所がなくなることが問題だ。ただ今後はこれらの問題よりも、電力配線を長くする弊害の方が影響が大きい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ