絶縁や寄生容量/配線抵抗の削減をどうするか?

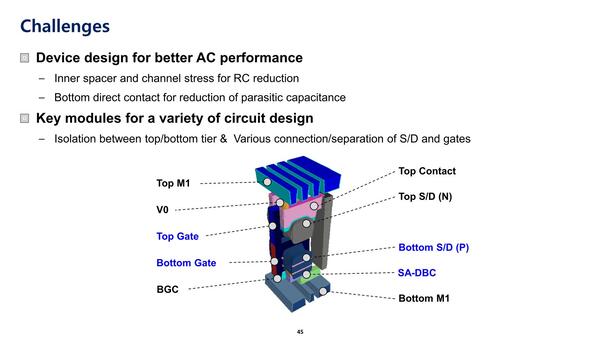

製造方法以外にもあるCFETの課題

製造方法をどちらにするかはおいておくとして、次からは共通の課題である。CFET構成では構造の密度が上がるがゆえに、より絶縁や寄生容量/配線抵抗の削減が課題になりやすい。

CFETの課題。絶縁性能を上げるために絶縁層の厚みを増やすと寄生容量の増加につながる。もちろん材料の改善である程度は改善できるにしても、最終的にはトレードオフになるので、どのあたりでバランスを取るかが難しいところだ

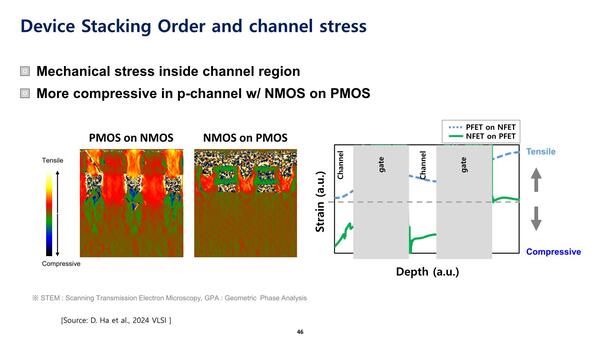

また前ページ2つ目の画像で、Stacking OrderとしてNMOS on PMOSが選ばれていたが、これを逆にするとどうなるか? というのが下の画像だ。

黄~赤が引っ張り応力(Tensile stress)、黒~青が圧縮応力(Compressive stress)をそれぞれ示す。PMOS on NMOS構造では、境界層における引っ張り応力がものすごく大きくなりがちになる

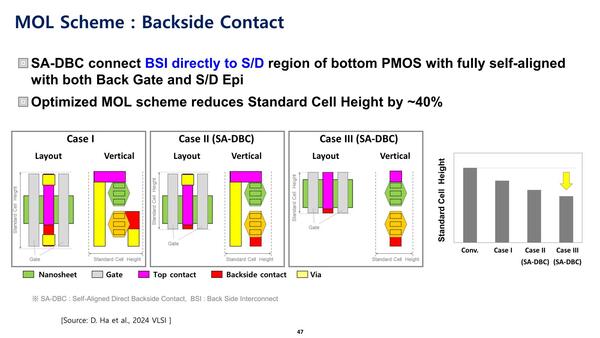

PMOS on NMOSにすると境界の圧力がかなり激しくなるので、NMOS on PMOSの方が好ましいとされる。またMOLの構築方法をどうするか? というのが下の画像。

Case IIIは一番実装密度を上げられるのは当然だが、ではTop ContactにどうやってBSからの配線をつなげるつもりなのかという問題が別途生じる。実装の容易さはCase Iが一番容易であり、そこからCase II/IIIと進むごとに難易度が上がり、一方Cell Heightは減るわけで、これもバーターである。どのあたりが着地点として妥当かを判断するのは難しい。

おそらくA5/A3/A2はこの方式が全部違うのだろう。例えばA5がCase I、A3がCase II、A2がCase IIIだとしても不思議ではない。

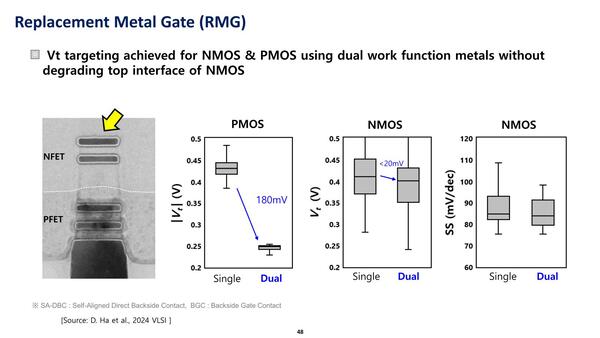

ゲートを、異なる2種類の金属を組み合わせるDWFM(Dual Work Function Metal)に置き換えることも有効だとしている。

もっともこれはCFETに限った話ではなく、なんならGAAどころかFinFETでも有効な話ではあるのだが、それがいまだに使われていないのは実際に利用するための課題がまだ多く残っているからで、これはCFETの時代までに実現できるようになってるといいな、という項目と考えた方がいいのかもしれない。

以上のように、現状CFETに関してはどう作り込むか、どういう構造/材料を使うかなど、まだ詰め切れていないところがある。そのあたりをGAA世代の間に詰めて、2030年台のCFET導入に間に合わせたい、と考えるのが正しいのだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ