2025年12月6日より10日にかけて、サンフランシスコで毎年恒例のIEDM(International Electron Devices Meeting)が開催された。IEDMはISSCCやHotChipsなどと異なり、LSIを構成する要素、つまりトランジスタ、配線、ADC/DACなどに焦点をあてた学会なので、ここで最終製品に関する説明はない。しかし、今後の半導体プロセスに向けた取り組みを知るという観点では貴重な情報源である。

これまでトランジスタ開発を牽引してきたインテルに暗雲

代わってSamsungとimecが今後のトランジスタを論じる

昨年はインテルが9本(うち2本は共同論文)を発表したが、今年はインテルのみでの論文が4本(10-1、23-6、32-1、36-2)と共同論文が2本(10-7、19-2)とそれほど多くなかった。

現在のインテルはあまりゆとりがないのだろう。2025年12月24日、NVIDIAがIntel 18Aの量産品への採用を見送ったとロイターが報じた。これも冷静に考えればおかしな話で、そもそもインテルは2025年8月頃にIntel 18Aでの外部顧客の獲得を断念したことがやはりロイターによって報じられている。

Intel 18Aを使うのは社内の製品(Panther Lake/Nova Lake/Clearwater Forest)および、米国政府との契約に基づく米軍や米政府機関向けの一部の製品に限られ、外部顧客向けにはIntel 18A-P/18A-PTやIntel 14Aになる予定だったからだ。おそらく今回のNVIDIAの話は本格的なものではなく、すでにPDK 1.0が存在するIntel 18Aを使ってなにかのチップを試験的に製造してみて、性能や歩留まりなどを確認した程度の話ではないかと思われる。

かつてはこうした試験的な製造は珍しいものではなかったが、昨今はNRE(Non-Recurring Engineering:一度きりの試作)コストの高騰化により、こうした試みは減りつつあるのは事実だ。ただ現在のNVIDIAの稼ぎからすれば、1回や2回の試作にかかる金額などたいしたものではない。NVIDIAにしても、本命があるとすればそれはIntel 18A-Pの方であり、そこに向けて実績を積む意味でまずは1回試作してみたという程度なのだろう。

話が逸れたが、以上のことから今回はインテルの発表は控えめであった。その代わりといってはなんだが、Samsungとimecがわりとがんばって今後のトランジスタの話をしていた。

まずショートコースでSamsungの"SC 1.1 Device Technologies for GAA Scaling and Emerging Alternatives"が今後のトランジスタの進化の方向を論じていた。Applied Materialsの"SC 1.3 Process Innovations and Materials to Sustain Moore’s Law in the Era of GAA and CFET"もロードマップ的ではあるのだが、Applied Materialsの講演は多分に構造よりも製造方法に振った内容になっていた。

テクニカルセッションではSamsungの"2.1 Gate-All-Around Technology for Sustainable AI: A Foundation for Future Logic Architectures"とimecの"2.3 3.5T CFET Block-Level DTCO for Superior PPA in A7 Node by Split Power, hDR Cells, Optimized Pins and BEOL"がわりと将来の話に近かった。そこで、SC 1.1の内容をベースにして、今後のロードマップについて簡単にまとめておこう。

imecのロードマップで見るトランジスタの未来

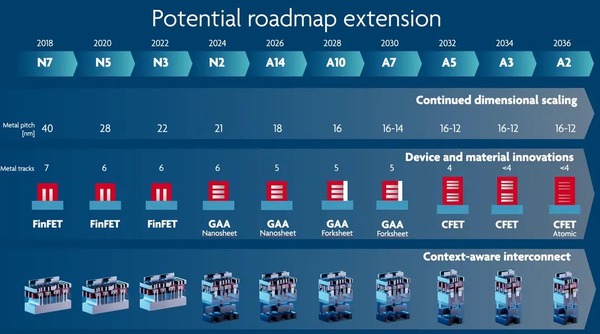

まず基礎知識として下の画像はimecの示す今後のプロセスロードマップである。imec、正式にはInteruniversity Microelectronics Centreという、ベルギーに拠点を置く独立系研究機関であり、シリコンスケーリングやシリコンフォトニクスなどを含む先端半導体研究を行なっている。

以前はITRS(International Technology Roadmap for Semiconductors)がこうした役割を担っていたが、2021年版のロードマップを最後に活動を終了。これに続きIRDS(International Roadmap for Devices & Systems)という組織がIEEE内に結成されたが、2024年度版がまだ完成していないという動きの遅さもあってか、あまり参考にされていない

imecには既存のファウンダリーやメーカーも協業しており、例えばラピダスも2023年にimecのコア・パートナー・プログラムに参加している。ここでN7~A2まで、おおむね2年おきにプロセスが革新されていく見通しを述べているわけだが、違いはご覧のように非常に小さい。

現在はFinFET(上の画像で言えばN7~N3)が全盛だが、このあとNanosheetを使ったGAA(Gate-All-Around)、すなわちTSMCのN2/A14やインテルの18A/14Aがやってくる。これに続き、GAAでもForksheetになるのがA10/A7世代。そして2032年頃にCFETに切り替わるという見通しを示している。先程の論文で言えば、imecの2.3は、2030年頃に登場予定のForksheet GAA、つまりCFET(Complementary Field-Effect Transistor)に変わる1つ手前のプロセスの詳細を論じているわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ