ロードマップでわかる!当世プロセッサー事情 第856回

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析

2025年12月29日 12時00分更新

前回まででHot Chipsの話は終わりなのだが、最後にHot Chipsでは出てこなかった話をしよう。それが何度かこれまでも言及してきた、ラックあたり600kWの消費電力となるKyberである。

NVIDIAの次世代ラックスケールシステムKyber(カイバー)

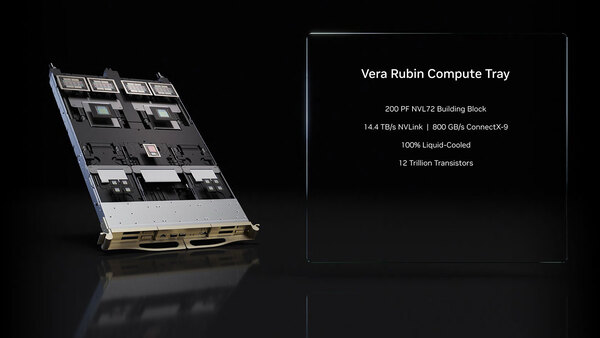

Kyberが初めて言及されたのは、2025年3月のGTCだったと記憶している。次世代GPUであるVeraとRubin CPUを組み合わせたVera RubinがNVL144として2026年後半に投入された。

その後継としてRubin Ultraを採用したものがKyber Rackに搭載される、ということが明らかにされた。スライドには出てこないが、Jen-Hsun Huang CEOが口頭で「消費電力が600kW」と説明している。

Rubin Ultra NVL576の詳細はまだかなり謎の部分が多いので、これを推察してみよう、というのが今回のテーマである。実を言うと、このあと5月に開催されたGTC Taipei 2025でKyber関連の展示があり、貴重な写真が何枚かあるので、このあたりを使いながらKyberに収められるNVL576の内容を解析したい。

まず基本的なGPUの性能をまとめたのが下表だ。「?」がついているのは筆者の推定である。

| GPUの性能比較表 | ||||||

|---|---|---|---|---|---|---|

| コード名 | コア名 | FP4 | FP6/FP8 | FP16/BF16 | FP32 | FP64 |

| Volta | V100 | 125TFlops | ||||

| Ampere | A100 | 312TFlops | 156TFlops | 19.5TFlops | ||

| Hopper | H100 | 2PFlops | 1PFlops | 0.5PFlops | 25.6TFlops | |

| Blackwell | B100×2 | 20PFlops | 10PFlops | 5PFlops | 2.5PFlops | 90TFlops |

| Blackwell Ultra |

B100×2 | 20PFlops | 10PFlops | 5PFlops | 2.5PFlops | 90TFlops |

| Rubin | R100?×2 | 50PFlops | 25PFlops? | 12.5PFlops? | 6.3PFlops? | 225TFlops? |

| Rubin Ultra |

R100?×4 | 100PFlops | 50PFlops? | 25PFlops? | 12.5PFlops? | 450TFlops? |

| Feynman | F100?×2 | 125PFlops? | 62.5PFlops? | 31.3PFlops? | 15.8PFlops? | 563TFlops? |

この表は各GPUのTensor Coreにおける性能を示したものであるが、RubinはNVL144がFP4で3.6EFlopsとあり、144ダイ(72GPU)で3.6Flopsなのでダイ1個で25PFlops、2つで50PFlopsと推定できる。Rubin Ultraはこのダイが4つで100PFlopsとなる。

FP4に関しては、NVIDIAの「世代ごとに2.5倍の演算性能向上」のルールがうまく適用されている。したがってFeynmanはこのルールを適用して125PFlopsと推定している。

一方でFP8については、FP4の1/3の性能であることが上2つの画像で示されているのだが、問題はこれはトレーニングだと明記されていることだ。NVIDIAの場合、トレーニングにはMixed Precisionを利用することがNVIDIAのWebサイトにも示されている。

たとえばFP8とFP16を混在させる形だ。この場合、性能はFP8とFP16の中間程度になるわけで、これがFP4に比べて2分の1ではなく3分の1になる理由と考えられる。逆にFP8のみでTensor Coreを使って推論を実行する場合、性能は2分の1であるとみなして上表のようになっている。

さて、表にして示したがこちらはあまり重要ではない。重要なのは次の表である。これはNVLinkの仕様を世代ごとにまとめたものである。

| NVLinkの仕様表 | ||||||||

|---|---|---|---|---|---|---|---|---|

| コード名 | コア名 | NVLink | 信号速度 | 配線数 | 変調方式 | 帯域(片方向 ・1 Link) |

Link数 | 帯域(双方向 ・全Link) |

| Volta | V100 | Gen 2 | 25GT/s | 8 Pair | NRZ | 25GB/s | 6 | 300GB/s |

| Ampere | A100 | Gen 3 | 50GT/s | 8 Pair | NRZ | 50GB/s | 12 | 600GB/s |

| Hopper | H100 | Gen 4 | 50GT/s | 4 Pair | PAM4 | 50GB/s | 12 | 900GB/s |

| Blackwell | B100×2 | Gen 5 | 100GT/s | 2 Pair | PAM4 | 50GB/s | 18 | 1800GB/s |

| Blackwell Ultra |

B100×2 | Gen 5 | 100GT/s | 2 Pair | PAM4 | 50GB/s | 18 | 1800GB/s |

| Rubin | R100?×2 | Gen 6 | 100GT/s | 2 Pair | PAM4? | 50GB/s | 36 | 3600GB/s |

| Rubin Ultra |

R100?×4 | Gen 7 | 100GT/s | 2 Pair | PAM4? | 50GB/s | 36 | 3600GB/s |

| Feynman | F100?×2 | Gen 8 | 100GT/s | 4 Pair? | PAM4 (多分) |

100GB/s? | 36? | 7200GB/s? |

もともとNVLinkはPascal世代のP100で導入したGPU同士の接続方法で、従来のSLIを置き換えた。もっともSLIは画面描画の分割といった用途向けなので、そもそも目的が違う。P100の世代はGPU同士を直接Point-to-Pointで接続する形であったが、V100世代から間にNVSwitchと呼ばれるNVLink用のスイッチを挟んで構成するようになった。もちろんBlackwellやRubin、Feynman世代もこのNVSwitchを挟んで接続する形になっている。

GTC 2025におけるロードマップ。Kyberの世代、Rubinには第6世代NVSwitch、Rubin Ultraには第7世代NVSwitchが充てられることが明記されている。Feynman世代は第8世代だ

NVLink 5の世代まではすでに情報が公開されているわけだが、Rubin世代のNVLinkはまだ不明である。ただ、Rubin世代は260TB/秒の帯域を持つ、と記事冒頭の画像に明記されている。1つのGPUから出るNVLinkの帯域は双方向で3600GB/秒である。260T÷3600G=72.2222であり、要するに72 GPUであり、ダイ数としては144なのでNVL144の名前なのだろう。

ここでもう一度、記事冒頭の画像の左側を見ていただくと、最上段にToRスイッチ、その下に電源を挟んで10本のComputation Blade、9本のNVSwitch Blade、8本のComputation Bladeと続いている。おそらくComputation Bladeには2組のVera Rubin Superchipが入り、NVSwitch BladeにはNVLink Switchが4組入るという形と考えられる。

なぜこう考えるかというと、2025年10月に開催されたGTC DC 2025における資料に、そのVera Rubin Superchipとそれを収めるComputation Blade、およびNVLink Switch Bladeが公開されており、スイッチは合計で4×9=36個となる。ということは、1つのRubinからは36本のNVLinkが出る計算になる。

逆に言えば36本で3600GB/秒なので、速度そのものはGen 5と同じく片方向あたり100GT/秒の信号のPAM4変調×2ペアで50GB/秒、双方向で100GB/秒という形の実装と考えられる。結果、NVL144のNVLink接続図は下図のようになる。配線量はNVL72の倍になる計算である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ