ロードマップでわかる!当世プロセッサー事情 第846回

Eコア288基の次世代Xeon「Clearwater Forest」に見る効率設計の極意 インテル CPUロードマップ

2025年10月20日 12時00分更新

Meteor Lakeと比べると電源配線の改善効果はあまりない

PowerVIAの構造は連載656回で一度紹介しているし、そのPowerVIAをIntel 4に実装した試みは連載727回で紹介している。要するに配線層の裏に電源供給層を設ける取り組みで、これはこれでいいのだが、問題はその電源供給層にどう本体側の電源層を接続するかという話である。

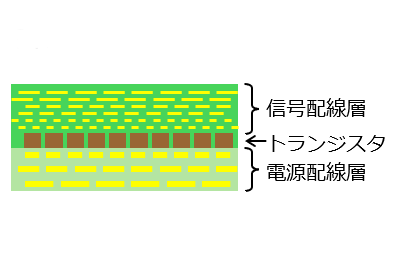

PowerVIAを使ったダイというのは下図のような構図になる。

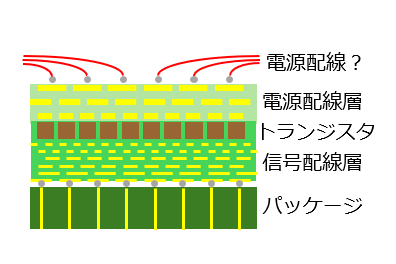

しかし、パッケージに実装するには上下をひっくり返した形になる。信号配線層の一番上(下図で言うなら一番下)にボールを取り付け、それでパッケージと接続するわけだが、では電源配線層をどうするか? という話で、まさか赤線のようにパッケージの上にワイヤーを飛ばすわけにもいかない。

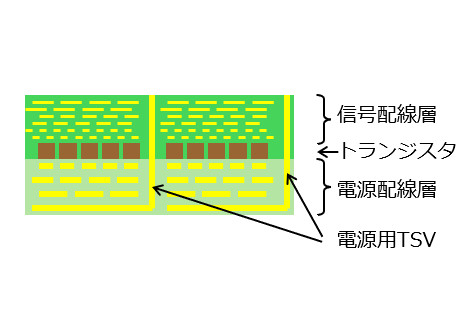

結局のところ下図のように、電源配線層からTSV(Through-Silicon Via)に接続し、信号配線層まで伸ばす必要がある。これをトランジスタごとにやったら裏面配線の意味がなくなるので、ある程度のブロックでまとめることで、VIAの本数を減らす工夫はあるだろう。

ただこういう仕組みになると、「トランジスタの真裏にキャパシタを置くことで電源供給を改善する」効果がかなり薄れてしまう。物理的に距離が離れているから、どうしても遅れが生じてしまうためだ。もちろん意味がないわけではないが、真裏にあるキャパシタは「電源容量こそ少ないがすぐ反応できる」のがメリットであり、VIA経由でとなると「電源容量が少なくいが、パッケージ側のキャパシタよりはすぐ反応できる」程度になってしまう。

おそらくMeteor Lakeのパッケージに比べると、電源改善効果はやや薄いことになるだろう。そのために結構大きめのダイを割いてベースタイルを作るよりは、いっそIntel 3にしてLLCを搭載してメモリーアクセス性能を改善した方がトータルで性能アップにつながる、という判断がなされたのではないかと筆者は考える。

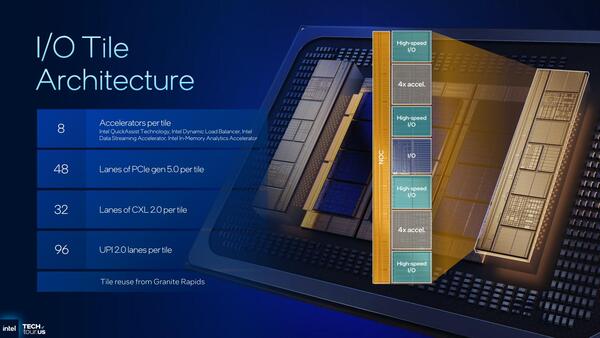

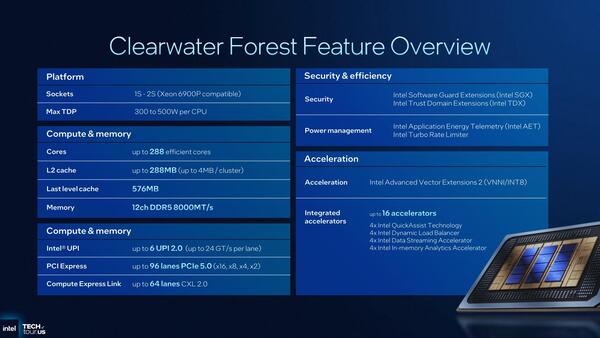

I/Oタイルは、Granite Rapidsのものそのままと説明がある。これは当然というか、更新されるのはXeon 7世代になるだろう。Granite RapidsのものであればAMXも利用できそうなものなのだが、無効化されているようだ。実際仕様一覧を見ても、AMXの名前がない。

実際仕様一覧を見ても、AMXの名前がない。LLCはアクティブベースタイル1枚あたり192MB(24×8MB)なので、3枚で576MBとなる。メモリーの説明はなかったが、8000MT/秒と言いつつMR-DIMMのサポートはなさそうである

ダイの製造原価はおよそ4000ドル

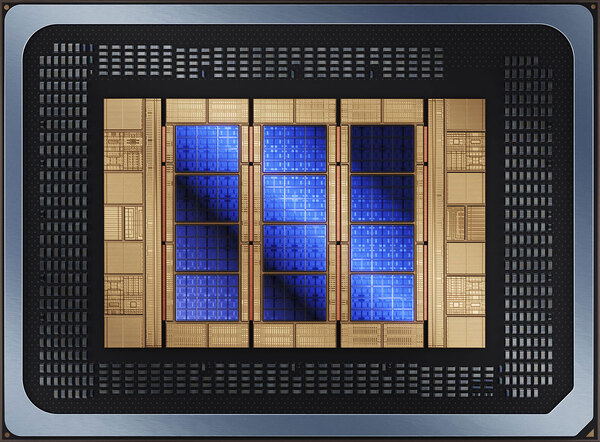

説明としては以上になるのだが、最後にダイサイズの測定をしよう。幸いインテルから高解像度の画像を提供されているので、ここからコンピュートタイルとアクティブベースタイルのサイズを推定してみた。

パッケージが既存のGranite Rapids(FCLGA7529:104.5×70.5mm)と同じと仮定すると、以下の試算となった。

| タイルの寸法(試算) | ||||||

|---|---|---|---|---|---|---|

| コンピュートタイル | 10.95×7.47mm= 81.80mm2 | |||||

| アクティブベースタイル | 14.50×39.72mm=575.94mm2 | |||||

Intel 3やIntel 18Aのウェハー製造コストがどの程度かは不明だが、TSMCが最近先端プロセスのウェハー処理コストを値上げしており、N2が3万7000ドル/ウェハー、N3が2万8000ドル/ウェハーと伝えられていることを考えて、仮にこれと同じ金額で製造でき、欠損密度を0.1個/cm2と仮定すると、以下の計算になった。

| ウェハーの製造コスト(試算) | ||||||

|---|---|---|---|---|---|---|

| コンピュートタイル | 1個あたり54.49ドル。歩留まりは92.20% | |||||

| アクティブベースタイル | 1個あたり672.73ドル。歩留まりは57.79% | |||||

アクティブベースタイルが異様に高価に思えるかもしれないが、600mm2弱だから仕方がない。コンピュートタイルが12個、アクティブベースタイルが3個必要になるので、EMIBでの接続やパッケージなどの実装コストを抜いた純粋なダイ製造の原価だけで2670ドル99セントとなる。これにI/Oタイル×2とパッケージ代と実装コストを追加すると4000ドルを下ることはないだろう。決してお安い製品にはならない、ということがうかがえる試算結果となった。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ