ロードマップでわかる!当世プロセッサー事情 第842回

双方向8Tbps伝送の次世代光インターコネクト! AyarLabsのTeraPHYがもたらす革新的光通信の詳細

2025年09月22日 12時00分更新

今週からHot Chips 2025の話題を説明するのだが、最初はチップではなくインターコネクトである。ここ4回ほど、Hot Interconnectsの絡みで光インターコネクトの話題が続いたわけだが、LightMatterやCelestial AIはHot InterconnectsとHot Chipsの両方で講演していた。そして、Ayar LabsはHot InterconnectsをパスしてHot Chipsだけで講演した。ということで光インターコネクトの最後として、Ayar Labsの講演を取り上げよう。

話題のAIインフラ向け光インターコネクト

Ayar Labs「TeraPHY」

Ayar Labsの名前は連載834回で少しだけ出た。同社はGlobalFoundriesのFotonixを利用してUCIeベースの光インターコネクトを開発しており、すでにいくつかの潜在顧客を獲得している。

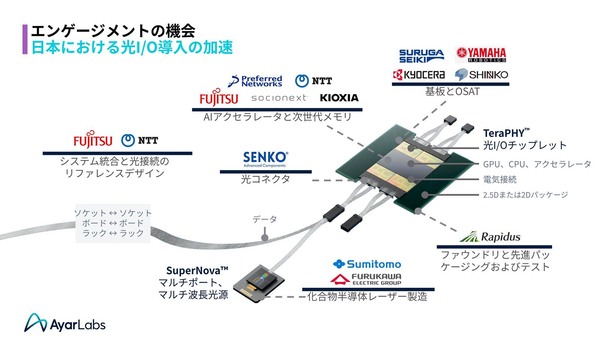

実を言うと今年6月にPlayground GlobalというDeep Tech特化型ベンチャーキャピタルが日本で説明会を開いたのだが、その時にPlayground Globalが出資している一社ということでAyar Labsの創業者兼CEOであるMark Wade氏も来日して簡単な説明をしている。

その発表会でのスナップ。中央にいるのがPlayground Globalの創業者兼General PartnerであるPeter Barrett氏、その右にいるのがAyer LabsのMark Wade氏である。ちなみにBarrett氏の左にいるのは、やはりGeneral Partnerに就任されたPat Gelsinger氏だ

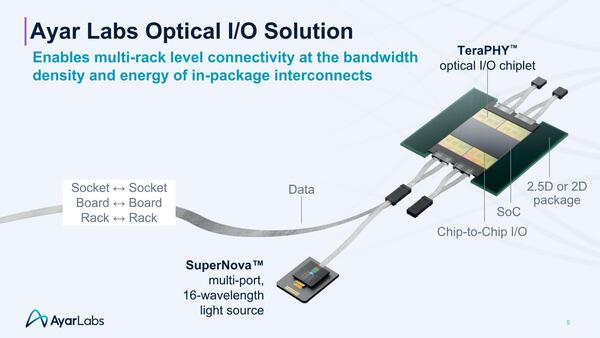

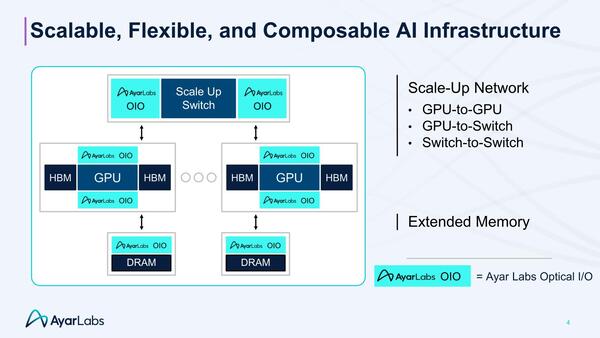

さて、Ayar Labsであるが、同社は2015年設立とこの業界では結構古参になる。当初から光インターコネクトの構築を目指しており、今では下の画像のような形でAIインフラを構築することを考えている。

DRAMを光接続で? と思うかもしれないが、IBMのPower10や11という例があるので、これも荒唐無稽とは言えない。というより、CelebrasのMemoryX/SwarmXよりレイテンシー少なくて済むのではなかろうか?(コストの問題はあるが)

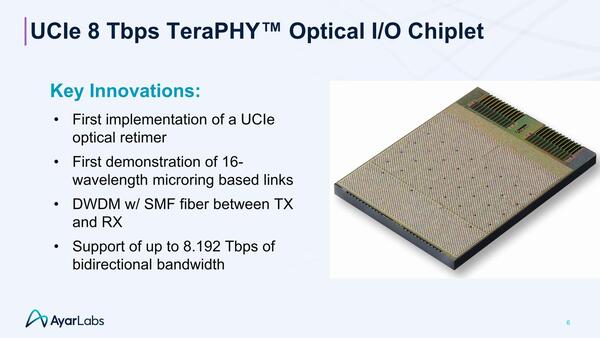

そんなAyar Labsが開発しているのがTeraPHYである。Ayar LabsはCPOをチップレットの形で提供しており、そのチップレットの名前がTeraPHYというわけだ。

TeraPHYの詳細が下の画像。ホスト、つまりASICから見るとUCIeのReTimerとして振る舞い、ただしその先は光信号でのやり取りとなる。したがって、ASICから見ると、単に長めの配線経由でチップレットがつながっているようにしか見えないことになる。

ここでおもしろいのが、DWDM(Dense WDM:高密度波長分割多重)を採用していることだ。実はAyar LabsのSuperNovaはCW-WDM MSA Consortiumという業界標準団体が策定した、CW-WDM MSA Technical Specificationsという仕様に基づいたレーザー光を出力している。

そもそもCW-WDM MSA Consortiumは2020年に業界11社(Arista Networks/Ayar Labs/CST Global/imec/Intel/Lumentum/Luminous Computing/MACOM/Quintessent/Sumitomo Electric/II-VI(現Coherent))によって形成された団体であり、目的はシリコン・フォトニクスを利用しての光インターコネクトを構築する際の光源を標準化しよう、というものである。

通信向けの光源に関して言えば、イーサネット向けのものが標準であり、必ずしも光インターコネクトに適したものとは言い難い。そこで、光インターコネクトに対応した新しい標準化規格を業界で作ろうというわけだ。

すでにv1.0の仕様がリリースされているが、9nm間隔は8+1/16+1の2種類、18nm/36nm間隔は8+1/16+1/32+1の3種類の波長が仕様の中で定められており、レーザー光源のメーカーはこれに対応した光源を出すようにすればよく、MRM/Detectorの方もこれに準拠する形だ。

ちなみに8+1というのはデータ用に8波+リファレンスクロック用に1波という話であり、これは16/32も同じである。波長はO-Band、1310nmを中心としている。例えば16+1波長で言えば、9nm間隔では1295.56~1304.58nm、18nm間隔では1291.10~1309.14nm、36nm間隔では1282.26~1318.35nmを利用することになっている。

話をSuperNovaに戻すと、SuperNovaそのものがどの間隔(9/18/36nm)を利用するかは公開されていないが、16波長のDWDMであることそのものは間違いない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ