ロードマップでわかる!当世プロセッサー事情 第841回

Gen1で3倍、Gen2で14倍の帯域幅を実現! Celestial AIのPFLinkがネットワークスイッチを劇的に進化させる

2025年09月15日 12時00分更新

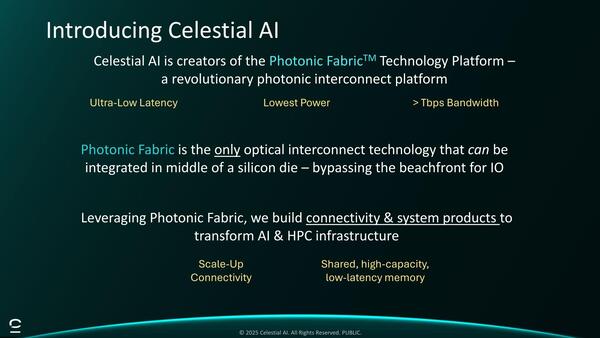

2025年8月21~22日に開催されたHot Interconnects 2025の解説、最後を飾るのはCelestial AIである。Celestial AIという社名であるが、同社は創業当時から光インターコネクトだけを開発している。紛らわしい感じもするが、その光インターコネクトのターゲットがAIプロセッサーやGPUであることを考えれば、間違っているわけでもない。ひょっとするとベンチャーキャピタルなどにはAIの文言を入れた方がウケがいいのかもしれない。

そんなCelestial AI、Hot Interconnectsではダイアモンド・スポンサーになったうえ、15分のスポンサー枠でRavi Mahatme氏(Senior Director of Product Management)が概略を説明するにとどまったが、Hot ChipsではPhilip Winterbottom氏(CTO)が"Celestial AI Photonic Fabric Module - The world’s first SoC with in-die Optical IO"と題した30分の講演を行なっている。そこで、両方の講演の内容をもとに説明していく。

LightmatterのPassageに近い構造だが

Celestial AIのPFLinkはCoWoSがベース

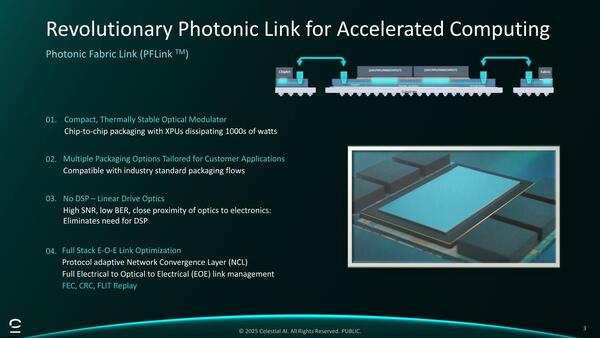

Celestial AIのターゲットは下の画像に示すように、Photonic Fabricの構築である。具体的にはチップ間接続とダイ間接続の両方をOpticalで行なうことを想定している。ちなみにこれはPFLinkという名称になっている。

beachfront(チップの周辺部)ではなく、ダイの中央からOpticalを出せる「唯一の」ソリューションとしているが、LightmatterのPassageがまさしくダイの中央からOpticalを出せるので、すでに唯一ではなくなっている

ここで消費電力数千WクラスのXPUと組み合わせても安定動作するというのはなかなか勇ましい数字ではあるが、これは後でモジュラーのところでもう一度触れる。またNo DSPがあるが、これも後述する。

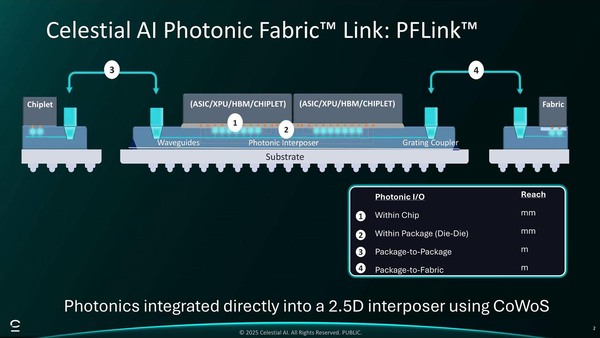

断面図をもう少し大きく示したのが下の画像である。TSMCのCoWoSをベースに、そのCoWoSの中にPICを組み込んで光信号の送受信を可能にする、という仕組みだ。なんというか、ものすごくLightmatterのPassageに近い構造であるが、これをCoWoSをベースにしているという点が大きく異なる。

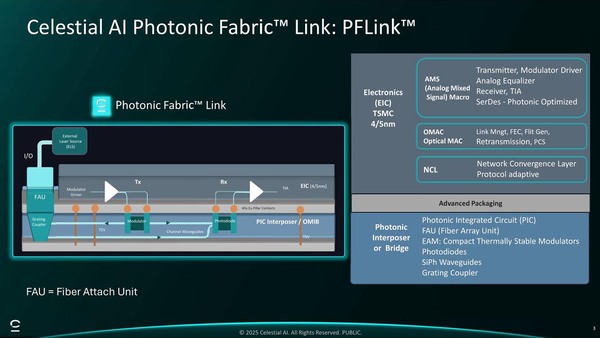

そのCoWoSをベースにした部分の、さらに拡大図が下の画像だ。インターポーザーの中にモジュラー/フォトダイオードを埋め込む形だ。またそのインターポーザー内に導光路も構築し、これを利用してダイ間の接続あるいはチップ間接続などを構築する形となる。

ただしインターポーザー内に埋め込むのはモジュラーとフォトダイオード、導光路とグレーチング・カプラー(FAUを接続するためのコネクター構造)などに限られるので、EICに関してはそのインターポーザーの上に載るダイの側に集積する構造を取ることになる。

ターゲットはTSMCの4/5nmということだが、これはとりあえずで、今後は3/2nmや逆に7/6nmへ対応を増やしていくことになるかと思われる。3/2nmはXPU本体向けに、7/6nmはI/Oチップレット向けにそれぞれ使われるようになるだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ