ロードマップでわかる!当世プロセッサー事情 第805回

1万5000以上のチップレットを数分で構築する新技法SLTは従来比で100倍以上早い! IEDM 2024レポート

2025年01月06日 12時00分更新

難点はウェハーの歪みだが

ダイサイズが小さくなれば無視できる

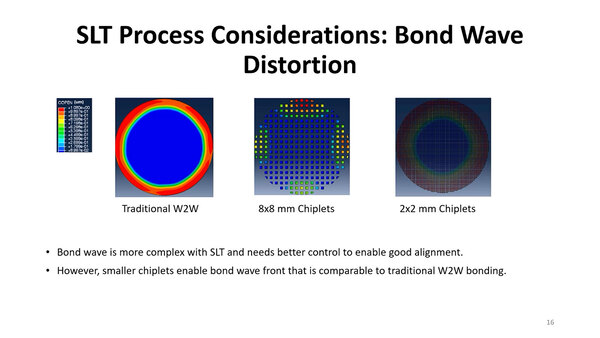

まだSelective Layer Transferの技術にはいくつか難点がある。その最大のものが、ウェハーの歪みである。

上の画像の一番左がなにもしない場合のウェハーの歪みで、当然端に行くほど歪みが大きくなる傾向にある。これは当然今回も発生するわけだが、インテルによればチップレットの寸法が小さくなればなるほど、WoWの場合と同じ状況になる、としている。

歪みそのものは今さらどうしようもない(これの改善は今回のテーマではない)が、その影響はダイサイズが小さくなれば、その問題は無視できるという話であった。WoWと同じ傾向になるので、WoWと同じ方法で対処すればいいわけだ。

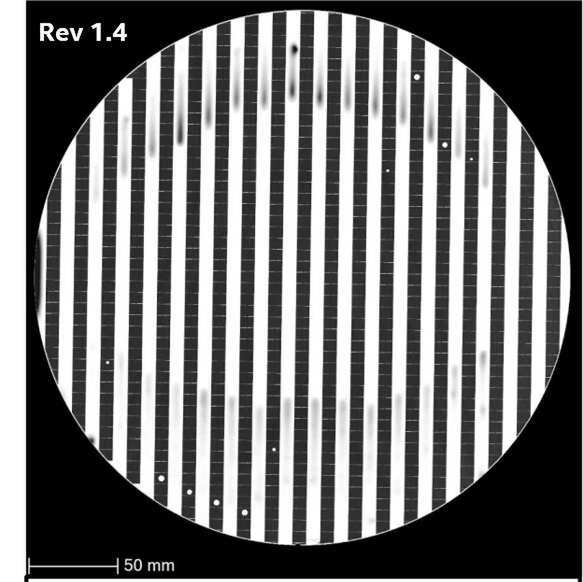

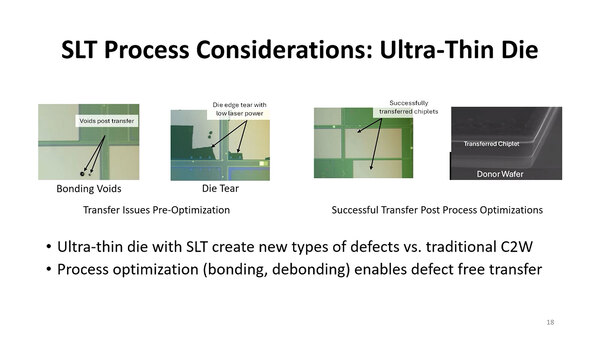

さまざまなパターンでの実装を試してみたが、概してうまくドナーウェハー上のダイがレシーバーウェハー側に転送できた、としている。

ペーパーによればチェッカーボードとストライプでやや影になっている部分があるのは、CSAM(超音波顕微鏡法)を使っての検査中に、2枚のウェハーの間に水が浸入してしまったことによるもので、Bondingそのものに問題はない、としている

ちなみにスライドでは省かれたが、論文の方には、ダイ同士の間隔が大きい場合に上手くいかなかった例が示されているが、これは設計の最適化で対処できるとしている。

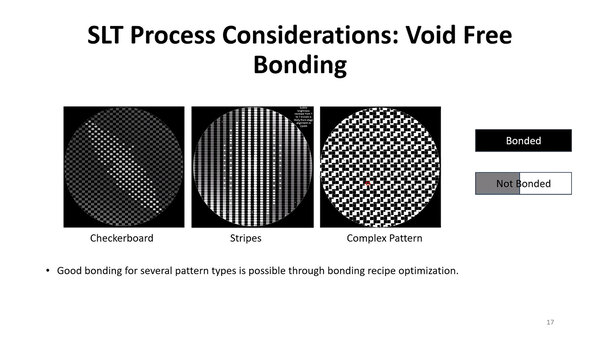

また他にも今回の技法の問題としてVoid(無効領域)の発生や、ダイの角の欠けなどが生じたケースもあるとする。ただきちんとパラメーターを合わせると、うまくダイを転送できることが実証されており、あとはプロセスの最適化を進めることで、これまでCoWでは発生しなかったこうした新しい問題の回避ができる、とまとめている。

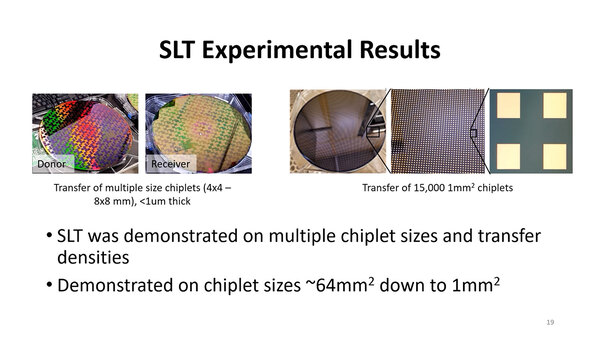

で、記事冒頭の画像に出てきたものが下の画像だ。今回の技法の実証用に作られたドナー(チップレット)とレシーバー(ベース側)のウェハーを組み合わせた結果が右側である。レシーバー側のベースダイの大きさは4×4mm~8×8mmまで複数のサイズの組み合わせとなっており、この上に1mm角のチップレットダイを転送するというものだ。最終的には1万5000個以上のチップレットを転送できたとしている。

WoWではベースダイとチップレットダイの面積が同じでないといけないので、チップレットダイが8×8mmにしないといけなかったが、今回は1×1mmのチップレットダイをWoWで積層できた、というのが一番下の文章の意味である

論文によれば、転送速度はおおむね毎時20万チップレットとしているので、今回の1万5000個のチップレットの転送にかかった時間は4.5分という計算になる。これは従来比で100倍以上の高速化になる、というのが今回の発表の肝である。

およそ200mm2以上のSoCなら

製造原価を大幅に下げられる

あくまでも今回は研究レベルの話なので、今すぐインテルの工場でこれを利用したサービスが可能というわけではない。ただこの方式が実用化されれば、チップレットの敷居がだいぶ下がることになる。実のところ、現時点でチップレットがメリットとして出てくるのは、モノリシックで200mm2前後以上のSoCに限られる。

例えばZen 4 RyzenではCCDが72mm2、IoDが122mm2なので、足すと194mm2になる。ギリギリ基準を下回るが、CCDが2個のRyzen 9では合計266mm2。

モノリシックでこれを作るとIoDの機能もTSMC N5での製造になるが、そもそもPHY(PCI ExpressやMemory I/Fなど)が含まれるからプロセス微細化の恩恵は受けにくい。強いて言えば内蔵するGPUが小型化されるのと、CCD/IoD間のインフィニティ・ファブリックのI/Fを省ける程度だが、それでも合計で200mm2を切るのは難しいだろう。

仮にモノリシックで200mm2(10×20mm)と仮定すると、1枚のウェハーから取れるのは最大300個、D0=0.1で有効ダイは240個となる(歩留まり80%)。ウェハーコストが1万7000ドルとして製造原価は70.8ドルほどになる。

一方チップレット方式では、CCDは876個中773個が有効となり歩留まりは93.1%、製造原価は22ドル。IoDは500個中429個が有効で、歩留まりは88.6%。製造原価は(TSMC N6の価格がTSMC N7と同程度だとすると)ウェハーコストは1万ドル程度なので、製造原価は23.3ドルほど。

これでRyzen 3/5/7のダイの製造原価は45.3ドル、Ryzen 9が67.3ドルということになり、Ryzen 9に関してはモノシリックとおおむね同等だが、Ryzen 3/5/7ではけっこうメリットになることがわかる。このあたりが現在チップレットを利用する場合の境であり、これより小さいものに関してはむしろ製造コストが上がることになる。

ただ今回の方式が広まれば、このしきい値(合計200mm2)をグンと下げられることにつながる。例えばSRAMの積層などを2層や4層にする場合でも、実装コストがそれほど増えないわけだ。

AMDの3D V-Cacheが32MB SRAMダイを2枚積層するのではなく、あらかじめ2枚のSRAMダイを焼き固めて1つの64MB SRAMダイにして積層する理由の1つは、この実装コストを最小に抑えるためだろうと考えられる。そう考えると、なかなか夢のある話であると言えるだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ