Hot Chipsで公開された新プロセッサーの説明の途中であるが、10月10日にAMDがAdvancing AI 2024というイベントを開催したので、今回はAMD CPUのアップデートをお伝えしよう。

イベントのレポートはRyzen AI Pro 300とEPYC 9005としてすでに既載されている。このうちRyzen AI Pro 300シリーズに関しては、今年のCOMPUTEXで発表されたRyzen AI 300シリーズのビジネス向けのPro版というだけで、仕様的にもすでに出荷中のRyzen AI 300シリーズと同じ(Pro機能の有無が異なるだけ)なのであまり説明の必要がないのだが、EPYCについてはけっこう細かい情報が公開されたので、こちらを中心に説明したい。

第5世代EPYCは16CCDが物理的限界

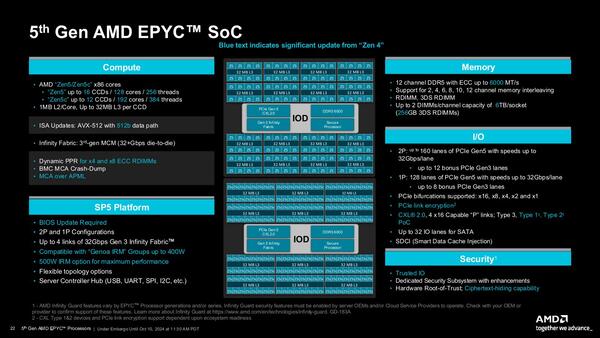

まずラインナップについてだ。連載776回で書いたように、TSMC N3を利用するのはZen 5cコアの場合のみで、Zen 5コアの方はTSMC N4となる。ここまでは想定通りであったが、IoDが予想通り大きく変更され、しかしながら筆者が想定していたMRDIMMのサポートは明示されなかった。その代わりだが、最大16個までCCDを接続できるようになった。

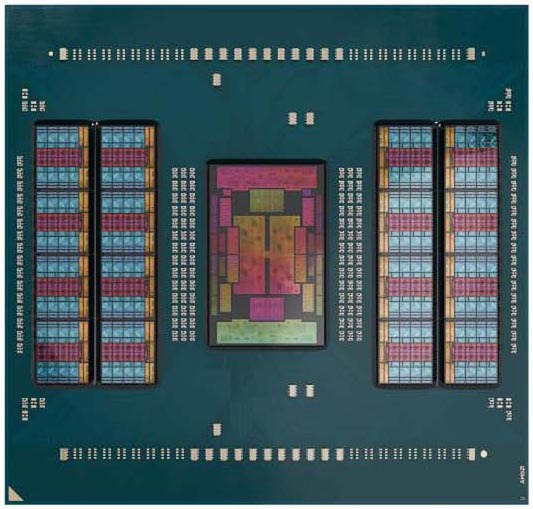

下の画像は少しわかりにくいが、中央の上半分がZen 5ベースのEPYC、下半分がZen 5cベースのEPYCである。

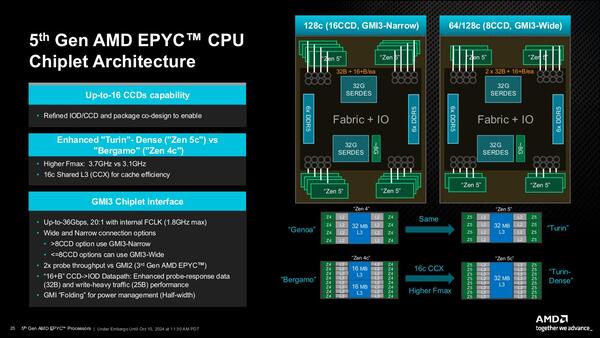

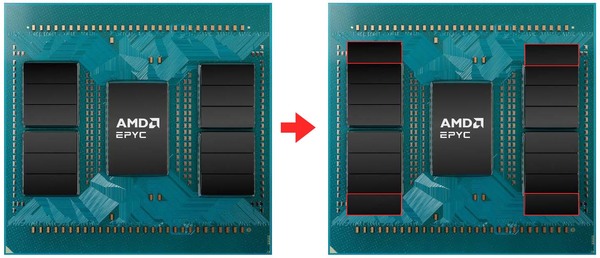

Zen 5ベースの場合、最大16個のCCDを接続可能で、この場合は128コア/256スレッドでの動作が可能になる。Zen 5cの場合は最大12CCDで、こちらでは192コア/384スレッドという計算になる。別にZen 5cではIoDに12CCD以上接続できないという話ではなく、物理的にSP5のパッケージに16個のZen 5cのCCDが載らないという制約から来るものと思われる。

左がZen 5cのパッケージ。右はこれに無理やりCCDを4つ追加したもの(赤枠の部分が追加したCCD)だが、明らかに配線面積が足りていない。この位置にCCDを追加するためには、パッケージの配線層を大幅に増やさないと厳しい(というか、増やしてもダメかもしれない)

これはZen 5のCCDの方も同じで、16CCDが上限であり、これ以上はパッケージを大きくする必要がありそうだ。

そうした話はともかくとして、IoDのインフィニティ・ファブリックのI/F(GMI3)はZen 4世代の12chからZen 5世代では16chに増やされた。もうこの時点でIoDは新しくなったことが明白である。

16 CCD/12 CCDのEPYCに関してはCCDとIoDが1本のGMI3で接続される形になるが、8CCDのEPYCに関しては2本のGMI3でCCDとIoDが接続される。この方式はGenoa世代でも採用されていたが、今回GMI3が合計で16ch分に増やされたことで、8 CCD以下の構成のEPYCはすべてこのDual GMI3(GMI3-Wide)構成での接続が可能になった。

SKUテーブルで言うと、64コアのEPYC 9575F以下の18製品がこれに該当する(ちなみにZen 5ベースのEPYCは全部で22製品なので、大半がGMI3-Wideの接続が可能になったことになる)。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ