ロードマップでわかる!当世プロセッサー事情 第764回

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ

2024年03月25日 12時00分更新

消え去ったI/F史は中断し、今回と次回は、3月18日からサンノゼで開催されたGTC 2024におけるNVIDIAの発表、特にBlackwellについて解説したい。

B100のダイサイズは850平方mm前後?

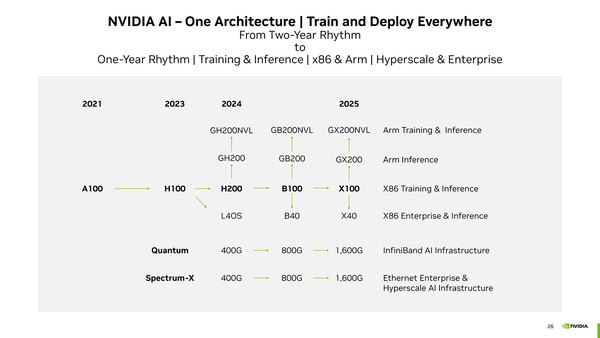

2023年10月に行なわれた投資家向けカンファレンスで示されたのが下の画像にあるロードマップである。今回GTC 2024で発表されたのはB100、つまりH200の後継となる新サーバー向けチップとこれを利用した派生型である。

昨年発表されたNVIDIAのロードマップ。H100とH200は同じ2023年に発表はされているが、発売は2024年ということでこのロードマップになっている。B100も今年中に発売される予定で、X100は2025年になる

最初にお断りしておくと、本稿ではB100とひとくくりに説明しているが、これは上の画像で"B100"と記されているのでこれを使っているだけで、実際にはB100/B200という2種類の製品名が混在、しかもB200には2種類のSKUがある「らしい」。

まだ正式に商品名とスペックが公開されていないので、ここではBlackwellアーキテクチャーを搭載したチップの総称として"B100"と説明することにする。

まずB100の元になるBlackwellチップであるが、製造はTSMC 4NPである。4N"P"がなにを意味しているのか公式には明らかにされていない。ただH100/H200世代は、TSMCのN4をベースにしたNVIDIAカスタム版であるTSMC 4Nプロセスを採用していた。

同じようにBlackwellでは、TSMCのN4P(N4の高性能版)をベースにNVIDIAカスタム版プロセスを利用しており、それがTSMC 4NPではないか? という気がする。トランジスタ数は1040億個で、H100が800億個と説明されていたので、3割程トランジスタ数は増えたことになる。

ちなみにダイサイズは後で推定するが、そもそもH100の時点でダイサイズは814mm2と発表されているため、単純に1.3倍にすると1058.2mm2となり、Reticle Limitをはるかに超えてしまう。トランジスタ数とダイサイズは単純に比例しない(構成によって変わる)から、実際にはReticle Limitの限界(26mm×33mmの858mm2)に限りなく近い程度に収まっていると思われる。

これは逆に言えば、SRAM(L1/L2/L3キャッシュ)の容量はH100からそれほど増えておらず、演算器のみ増やした、あるいは演算器の複雑さが増したことを示唆していると考えられるが、このあたりはホワイトペーパーが出てもう少し正確な情報が手に入らないとはっきりしたことは言えない。ただ"The Largest Chip Physically Possible"とまで言ってるので、限界にチャレンジしたのは間違いなさそうだ。

ちなみに純粋に技術的に言えば、Reticle Limitを超えるサイズのダイを作ることは不可能ではない。例えばチップの上半分と下半分に分けて、それぞれ別のマスクで露光をすることで、Reticle Limitを超えるダイを露光することは可能だ。

ただしその場合、2回の露光のずれが1nm未満のオーダーで一致していないと、使い物にならないチップもどきが完成する。しかもこれをトランジスタ層(ここだけで10回を超える露光がある)だけでなく配線層まで全部実行するので、露光の回数は下手をすると3桁に行きかねない。

このどこか1回だけでもずれたらパーなわけで、歩留まりは猛烈に低いと予測できる。したがって、さすがにそこまでの冒険はNVIDIAもやらないだろうし、そう考えるとダイサイズはReticle Limitにかなり近い数字、850mm2前後になるだろう。

Blackwellのダイはかなり大きいが、B100はこのBlackwellのダイを2つ組み合わせた格好となる。要するにAMDのInstinct MI250Xと同じ構成である。2つのダイの間は独自のインターコネクトで接続される格好だ。

Full-cache coherencyの意味は、2つのダイのおそらく2次キャッシュ同士をダイの外で接続しているものと思われる。もともとHopperの世代では、2次キャッシュは物理的に2つに分割され、これがダイの内部でつながっている構造だった。

B100では、1つのダイには2次キャッシュが1つのブロックとして構築されているが、2つのダイの2次キャッシュが外部のインターコネクト経由で相互接続されているのだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ