前回の冒頭でも少し触れたが、AMDは6月13日にData Center and AI Technologyというイベントを開催した。

この様子はYouTubeで視聴可能(ただし1時間半:ダイジェスト版は3分48秒)であるが、ここでBergamoとGenoa-Xという新しい第4世代EPYCと、さらにInstinct MI300シリーズの若干の詳細、それとPensandoベースの新製品紹介などがあった。今回はこの中からBergamoとGenoa-Xの詳細について解説しよう。

3次キャッシュを増やした第4世代EPYC

Bergamo

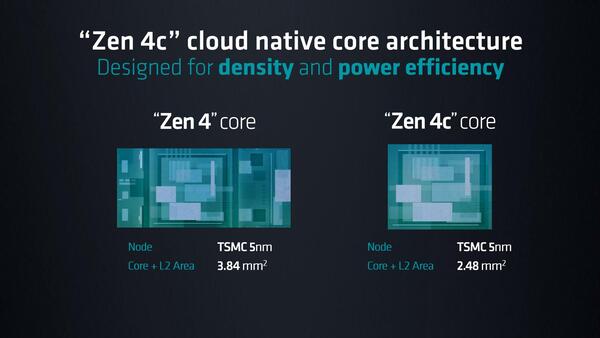

BergamoはZen 4cコアを128コア搭載する、という話はすでに公式にも語られていたが、このZen 4cとZen 4の違いは3次キャッシュの容量のみである、という話を連載696回にお届けした。さてその答え合わせであるが、論理的にはこれは正確ながら、物理的にはやや間違っていた。今回公開された話は以下の3つであった。

- CPU Coreそのものは論理的にはZen 4そのままながら、物理設計をやり直してエリアサイズを縮小。

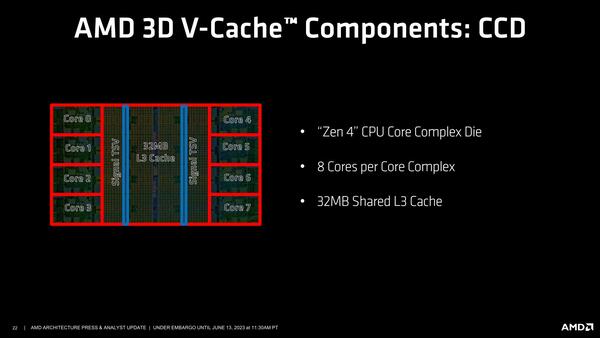

- 3次キャッシュは従来の4MB/コアから2MB/コアに縮小。また3次キャッシュには(3D V-Cacheを利用した)容量拡張オプションは用意されない。これにともない、TSVエリアは存在しない。

- CCXの構成そのものは8コア/CCXで変わらず。したがってBergamoでは1つのダイに2つのCCXが搭載される。なおこの2つのCCX同士はローカルで通信するのではなく、IoD経由での通信となる(要するにZen/Zen 2世代と同じ)。

まずは物理設計の話。俗にPPA(Power, Performance, and Area) Optimizationなどと言うが、物理設計を行なう際に動作周波数のターゲットをどのあたりに置くかで消費電力やエリアサイズが変わってくる。

これはセルライブラリーに高密度・低消費電力のものを使うか、高速のものを使うかという話であり、クリティカルパス(プロセッサーの動作速度を決める、一番タイミング的にシビアな部分)には高速のライブラリー、それ以外のところは高密度・低消費電力のものを使うというのが一般的ではあるが、「どの程度使うか」は設計者のサジ加減次第であり、最終的にどの程度の周波数をターゲットとするか、あるいはダイサイズをどの程度に抑えたいか、消費電力をどの程度にするか、などでサジ加減が変わることになる。

Zen 4cの場合、CPUコア+2次キャッシュのサイズをZen 4と比較して35%縮小した。またZen 4ベースのEPYC 9654が96コアでTDP 360Wなのに対し、Zen 4cベースのEPYC 9754は128コアでTDP 360Wだから、ラフに言って25%消費電力を削減している計算になる。

実際にはIoDの分もある(IoDは完全に同じものだそうである)ので、もう少し消費電力の削減分は大きいかもしれない。その反面、動作周波数はEPYC 9654がベース2.4GHz/最大ブースト3.7GHzなのに対し、EPYC 9754はベース2.25GHz/最大ブースト3.1GHzと低めになっているのは、コアそのものを高密度/低消費電力向けに振った副作用ともいえる。

ただコア数×動作周波数という理論的な演算性能で言えば、EPYC 9654 vs EPYC 9754は以下のとおりで、EPYC 9754の方がむしろ高めである。動作周波数を抑えてコアの数を増やしたことが功を奏した格好だ。

| EPYC 9654 vs EPYC 9754 | ||||||

|---|---|---|---|---|---|---|

| ベースクロック | 96×2.4 : 128×2.25 = 1 : 1.25 | |||||

| 最大ブーストクロック | 96×3.1 : 128×3.70 = 1 : 1.12 | |||||

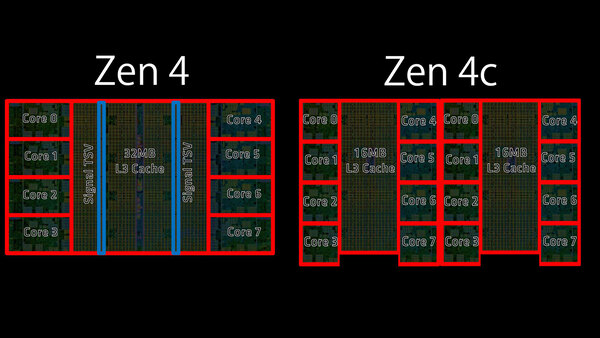

次が3次キャッシュのサイズである。下の画像はZen 4とZen 4cの差を示したものだが、先に書いたとおりコアそのものの論理設計はまったく同一だそうで、違いは3次キャッシュの容量のみということになる。

連載696回の画像はZen 3とZen 4の比較だった。今度はZen 4 vs Zen 4cである

その3次キャッシュだが、さすがにここはZen 4でも高速向けのセルライブラリーを使うことはなく、高密度/低消費電力のセルライブラリーを使っていると思われるので、3次キャッシュの再設計でも単純に面積が半分弱になるだけと考えられる。

「弱」なのは上でも書いたがZen 4cでは3次キャッシュにTSVエリアがなくなる。下の画像はZen 4の3次キャッシュの構造を示したスライドであるが、これを元にしたZen 4cの推定図がさらにその下の画像である。Zen 4のダイサイズが70mm2とされるのに対し、この推定図によればZen 4cのダイサイズは78.3mm2ほどになると計算される。

Zen 4cの推定図。いつもの継ぎ接ぎワーク。記事冒頭のZen 4cをZen 4と比較した画像を元にすると、コア+2次キャッシュは幅0.6倍、高さ1.08倍になっていると推定して変更。3次キャッシュは単に半分にしたが、実際はコアの高さが変わっているのに合わせてレイアウトを再設計しているかもしれない(やってない気はするが)

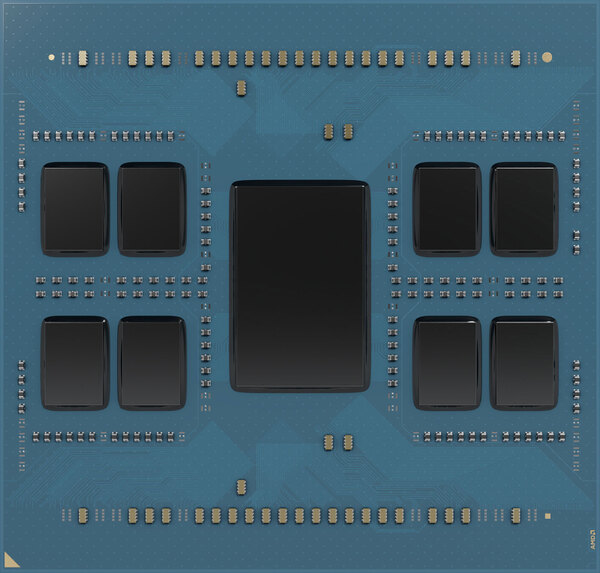

一方でAMDによるBergamoのCGから同じように寸法を割り出すと、おおよそ74.9mm2程で、筆者の推定はやや大きめであるが、なんにせよ75mm2前後ということで、GenoaのZen 4のダイからわずかなダイサイズの増加でコア数を倍増できたことになる。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ