製品ラインナップは3種類

このAD1028なりAD2056なりはIPの形で提供する予定であり、自身でチップを提供する計画は2020年の時点では存在していなかったようだ。ただそこから2年経った2022年1月、VSORAはTyrチップの発売を発表する。

ラインナップとしてはローエンドのTyr 1とミッドレンジのTyr 2、ハイエンドのTyr 3の3つが現在あがっている。

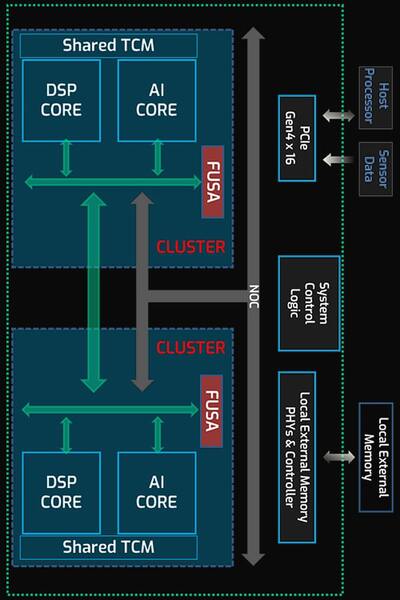

これは内部構成の違いであるが、TyrではAD1028の流れを汲むClusterという新しい処理ブロックが定義された。このClusterにはDSPコアとAIコア(前ページ最初の画像でいうことろのDLA)が搭載されており、Clusterあたりの性能はDSPコアが512 ALU、AIコアが32K MACである。これと13MBの共有TCM、それとFUSA(FUnctional SAfety:機能安全)ユニットから構成される。

TyrプロセッサーはこのClusterに加えて、外部メモリーコントローラーやPCIeコントローラー、制御用プロセッサーが搭載される格好だ。

ラインナップは下表のとおりで、あとはどの程度の演算性能が必要かで選べばいい。

| Tyrプロセッサーのラインナップ | ||||||

|---|---|---|---|---|---|---|

| 製品名 | 性能 | |||||

| Tyr 1 | Cluster数2。64K MACと1024 ALUで演算性能260TFlops(Sparsityで516TFlops) | |||||

| Tyr 2 | Cluster数4。128K MACと2048 ALUで演算性能520TFlops(Sparsityで1032TFlops) | |||||

| Tyr 3 | Cluster数8。256K MACと4096 ALUで演算性能1040TFlops(Sparsityで2064TFlops) | |||||

ちなみにFUSAユニットというのは、障害対策のユニットである。自動車の中でも、特に運転に直接関係する部分では機能安全という考え方が取り入れられており、ISO 26262と呼ばれる規格の中でASIL-A~Dまで4レベルの安全水準が定められており、機能や用途に応じてどの水準を満たすべきかが定義されている。

問題はこのうちASIL-Bくらいまでであれば、自動車向けのプロセスと呼ばれるものを使えば故障率を要求水準内に抑えられるが、一番厳しいASIL-Dの場合はこれを満たすのは現状不可能である。

ただし逃げ道があって、複数のユニットを同時に動作させ、片方がおかしくなったらそちらを切り離して正常なユニットで処理を継続する、という実装にすることで要求水準を満たせる。ただしその場合以下の処理を行なう機構が必要である。

- 複数のユニットを協調して動作する

- 故障/障害を検出する

- 故障/障害がどのユニットで発生したかを判断する

- 故障/障害を発生したユニットを切り離す

FUSAはこれを担うものであると考えればいい。DSP部のALUの数とDLA部のMACユニットの数の比率がAD1028と異なるのだが、これはおそらく顧客からのニーズのフィードバックと考えられる。要するにセンサーからの取り込みの処理性能をもっと引き上げる必要があった、というわけだ。

Tyr 1~3とラインナップが3つあるのは、そもそもVSORAがL2~L5までの自動運転とターゲットを広げたためで、Tyr 1はL2の、例えばレーンアシストとか道路標識の認識と通知といった簡単な用途向け。一方Tyr 3はL5の自動運転に向けたもの。その中間がTyr 2と思われる。

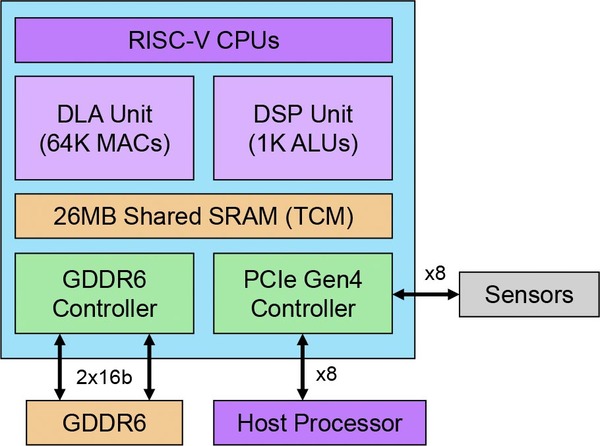

上の画像はTyr 1の内部構造で、制御用プロセッサーにはRISC-Vを、外部メモリーは32bit幅のGDDR6を使うとしており、センサーやホストとの接続はPCIe x8構成となっている。ちなみに消費電力はTyr 1が13W未満、Tyr 3が50W未満とされており、Tyr 2はおそらく25Wかそのあたりと想像される。

競合製品(例えばNVIDIAのOrin)と比べると、センサー用のフロントエンド(カメラ用のISPなど)がないなど、制御プロセッサーが本当に最小限の能力なので、Tyrの上位に強力な判断用のプロセッサーが必要など、いろいろ欠けているものもあるが、その一方で本当に最小限必要な要素をまとめているので、むしろカスタマイズがしやすいという見方もできる。

VSORAによれば2022年第4四半期中にサンプル出荷を開始し、量産車には2024年に搭載される見込みとしているが、さてどこまで市場に食い込むことができるのだろうか?

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ