ロードマップでわかる!当世プロセッサー事情 第673回

インテルがAIプロセッサーに関する論文でIntel 4の開発が順調であることを強調 AIプロセッサーの昨今

2022年06月27日 12時00分更新

今年6月13日から開催されたVLSI Symposium 2022はいろいろ話題が多く、例えばインテルはIntel 4の詳細を公開していたりする。この話はまた改めてきちんと説明するが、インテルは今回全部で15もの発表を行なっている。もっともこの中にはShort Course(技術講座)の分も含まれているので、論文そのもので言えば12本となっている。

論文の中に、“[C08-1] An 8-core RISC-V Processor with Compute near Last Level Cache in Intel 4 CMOS”と呼ばれるものがある。これだけ見ると「Intel 4プロセスを使ったRISC-Vコア?」ということでちょっとびっくりしたのだが、中を見ると「そりゃRISC-V使った方が楽だよね?」という、分類としてはAIプロセッサーに属するものだった。

これはあくまで研究レベルの話で、そのまま製品になることはなく、将来のx86プロセッサーに応用される「かもしれない」レベルの話であるが、なかなかおもしろかったので解説したい。

Intel 4プロセスのAIプロセッサー

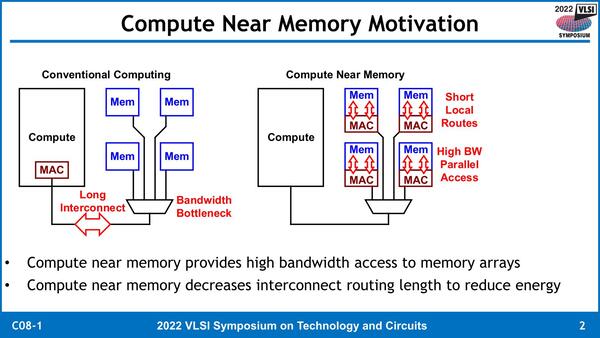

さてこの論文であるが、タイトルの中で重要なのは“An 8-core RISC-V Processor”でも“in Intel 4 CMOS”でもなく、“with Compute near Last Level Cache”である。要するに分類としては、連載668回でも触れたPIM(Processor In Memory)の延長にある。

ただPIMはメモリベンダーには容易なソリューションなのだが、そうでないとまずメモリーを構築するところから始まるので大変である。これに対して、Last Level Cacheは、インテルで言えば3次キャッシュに演算ユニットを突っ込むのはそれほど大変なことではない。

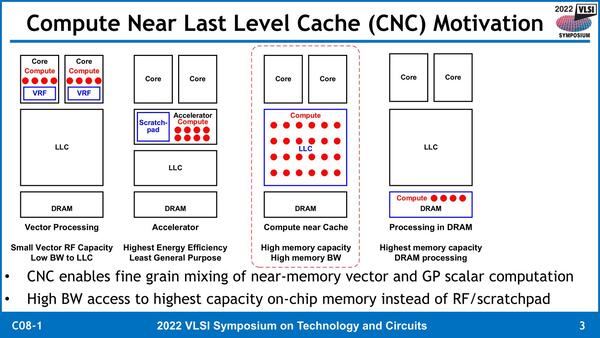

さて、もうすこし厳密にCompute Unitをどこに入れるか? を検討したのが下の画像だ。CPUコア内に置くのが一番悪手というのはわかるとして、アクセラレーター/LLC/DRAMのどこで置くのがベターか? というのはエネルギー効率、容量、帯域の観点でトレードオフの関係になる、としている。

インテルは今回、LLCの中にCompute Unit(CNC)を実装することで、それなりに高い演算性能とメモリー帯域・容量をバランスよく利用できるようにする選択肢を選んだ格好だ。

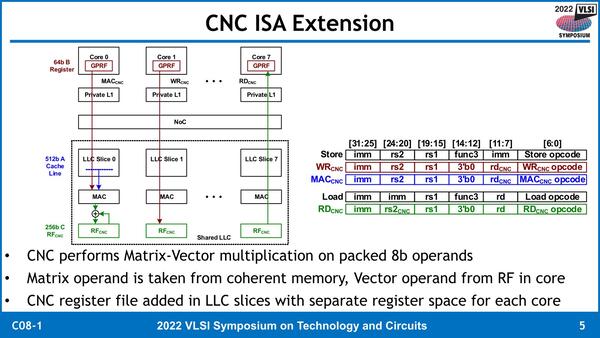

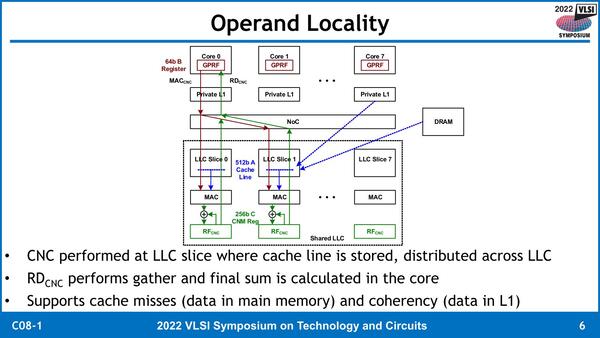

この効果を試すためのプラットフォームとしてインテルはRISC-Vコアを選んだ。この構図はCoreアーキテクチャーのRing Busを彷彿させるが、厳密にはRing Busではなく2D Meshの構成になっている。8つの64bit RISC-Vコアに、それぞれ64KBのSRAMとCNCを組み合わせて配する格好で、2次キャシュ(今回の構成はRISC-VはL1 I/D-Cacheのみ搭載されている)の合計は512KBになる。なんというか非常に小規模なコアである。

ここに搭載されるCNCであるが、256bit幅の比較的単純なSIMDで、演算も可能なのはMAC演算のみである。命令も演算(MACCNC)以外にLLCからのロードとLLCへのストアー(Load/Store)、CNC用のRF(Register File)への書き込みと読み出し(RDCNC/WRCNC)の5種類のみとなっている。

もちろん演算そのものはCNCに隣接したLLCとの間でしか行なわれない形になっている。

演算の詳細そのものはこちらのスライドでは明記されていないが、論文の方を読むと“CNC multiplies an 8×8 INT8 Matrix by an 8×1 INT8 Vector and accumulates the INT32 result in RFCNC”とあるので、INT8の8×8の行列と8×1行列の乗算を行ない、その結果をINT32としてCPUコアの側の汎用レジスターに送り出す、という処理をするとしている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ