ロードマップでわかる!当世プロセッサー事情 第655回

Alder Lakeと十分戦える省電力機能が実装されたRyzen 6000 Mobileシリーズ AMD CPUロードマップ

2022年02月21日 12時00分更新

2月17日にAMDはRyzen 6000 Mobileシリーズの詳細を公開した。概略はKTU氏の記事が上がっているので、それを読んで全体を把握いただくとして、この記事ではアーキテクチャーとその他細かい話をお届けしよう。

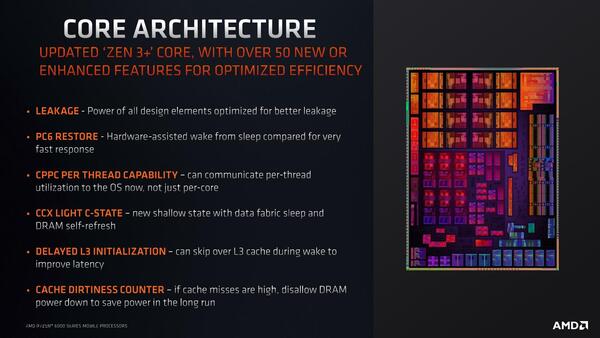

まずZen 3+コアについてだ。Joe Macri氏(Corporate VP兼Product CTO)が明確に「性能改善そのものの変更はない」と説明しており、同一周波数ならばRyzen 5000シリーズとほぼ同じ性能(正確に言えば3次キャッシュ容量がCCXあたり32MB→16MBに減っている分、場合によってはやや下がる可能性がある)と考えられる。ではなにが変わったか? というのが下の画像だ。

これを順に説明していこう。

Leakage(リーク電流削減)

そもそもTSMCのN7からN6に変更したことでトランジスタ密度がおよそ18%ほど向上するとされているが、実はこれも少し怪しい。というのは、TSMCはN6プロセスに関して、RTO(Re-TapeOut)とNTO(New TapeOut)の2種類の方式があると説明している。

要するにN7を利用して設計したデザインをN6に持っていくにあたって、N7のマスクをそのまま再利用する方式(RTO)と、改めてN6に最適化したマスクを作り直す方式(NTO)があり、18%の向上効果が得られるのはNTOの場合だからだ。

RTOの場合でも、配線層のEUV(極端紫外線)露光がN7+世代より1層増えて5層分をEUV露光で行なう関係で、歩留まりは向上するとされる。画像の出典はTSMCのウェブサイトにあるN6のページより

もっとも今回の場合、Zen 3→Zen 3+ではかなり細かな変更が多いので、物理設計のやり直しは当然発生しており、必然的にNTOを採用したと思われるため、その分ダイサイズは小型化しているとは思う。

話を戻すと、ダイサイズを小型化したとしても、トランジスタの構造そのものはN7とN6で基本的に同じである。「基本的に」というのは、ArF+液浸のマルチパターニングに比べてEUVで露光した場合、パターンがよりエッジの効いた形になるので、より精度が高いトランジスタを構成できると思われ、これにより若干特性の変化はあるからだ。

といっても、基本的なFinFETの構成そのものは変わらないので、リーク電流の特性などもN7と大きくは変わらないだろう。ただそのままではRyzen 5000シリーズと消費電力が変わらないことになる。

ここでもう一度最初の画像に話を戻すと、“Power of all design elements optimized for better leakage”とあるあたり、そもそもCell Libraryそのものを高速化ではなく省電力化に振ったものを利用していると思われる。

もともとAMDはTSMCやGlobalFoundriesなどファウンダリーが用意する標準のCell Libraryを使わずに、自社でCell Libraryを用意して利用するメーカーだったが、今回TSMC N6向けには省電力のCell Libraryを用意して、これを全面的に利用することにしたというように読める。

この場合の代償は動作周波数の頭打ちが低くなることだ。実際Ryzen 6000シリーズのSKUを見てみると、Ryzen 7 6800HがBase 3.2GHz/Boost 4.7GHzで45W、一方Ryzen 9 6900HXがBase 3.3GHz/Boost 4.9GHzでTDP 45W+とあるあたり、おそらく3.3GHzあたりから急激に消費電力が増える格好になっているものと思われる。ただこうしたピークの消費電力を抑えてでも、通常時の消費電力を抑えたかったのだろう。

PC6 Restire

(スリープからの復帰時にハードウェアサポートを追加)

PC6というのはCPUの動作モードの1つで、以下の構成である。

| PC6の動作モード | ||||||

|---|---|---|---|---|---|---|

| CPUコアへの電力供給 | Off | |||||

| L1/L2 | 内容をメモリーに書き出して電源Off | |||||

| L3 | 部分的に内容をメモリーに書き出して電源Off(実装によっては部分的に保持) | |||||

ここから復帰させてC0(フルに稼働状態)に持っていくのにそれなりの時間がかかる。ただし待機時電力が大幅に減るので、可能であればC1やC1EではなくPC6にした方が省電力につながるが、ただマウスを動かしてから画面が復活するまで数秒から数十秒かかるというのは使う側からはストレスである。

そこでこの画像でいうところのWake Timeを短縮するようなハードウェアを新規に追加することで、C6からの復帰を高速化し、ストレスを減らしたという格好だ。

CPPC per Thread capability

(PPCをスレッドごとに実装)

CPPCの話は連載516回で触れたが、OSがプロセッサーの動作速度を制御する際のメカニズムで、ACPI 5.1で初めて入り、ACPI 6.0ではCPPC2というより機能が拡張されたものになっている。AMDはZen 3でCPPC2を搭載したが、この際の実装はコアあたり1つのエントリーになっていた。これに対してZen 3+ではこれをスレッド単位(つまりコアあたり2つのエントリー)とすることで、さらに動作周波数変更時のオーバーヘッドを減らしたとする。

CCX Light C-State

(CCX向けの軽いC-Stateを追加)

CCXは8つのZen 3コアと3次キャッシュが相互接続され、さらにインフィニティー・ファブリックのI/Fが集約されているが、この3次キャッシュとの接続やインフィニティー・ファブリックのI/Fに、軽いWait State(先の画像で言えばC1Eに当たるようなモード)を新たに追加したようだ。これによって、例えばコアは動いていても3次キャッシュとインフィニティー・ファブリックにアクセスしないようなケースで細かく消費電力を下げることが可能になった。

Delayed L3 Ininitialization

(3次キャッシュの遅延初期化)

2つ前の画像で言えば、PC6(Package C6)ステートに入っている場合、3次キャッシュの内容も破棄されている。したがってPC6からC0に復帰する場合には、一度3次キャッシュの内容も全部初期化する必要があるのだが、初期化が終わるまで待っていると時間がかかりすぎる。

そこでコアの復帰と3次キャッシュの初期化を並行して行なうことで、とりあえずトータルの待ち時間を短縮したという仕組みだ。もちろん初期化が完全に終わるまでは3次キャッシュやメモリーアクセスができないが、

CPU #0~#7初期化→初期化完了を確認→3次キャッシュ初期化→初期化完了を確認→稼働

という流れが

CPU #0~#7初期化→初期化完了を確認-+→稼働

3次キャッシュ初期化--→初期化確認-+

という具合に、3次キャッシュとCPUコアの初期化を並行して行なえる分、待ち時間がやや削減でき、それだけ高速に復帰できる。

Cache Dirtiness counter

(キャッシュのヒット率確認)

反応時間を優先するための措置である。キャッシュのヒット率がしきい値以下に下がった場合は、しばらくの間はメモリーアクセスを行なって内容を最新のものに更新しないとプロセッサーそのものの処理がメモリーアクセス待ちに入ってしまう。

こうした状態ではDRAMのパワーダウン(というよりメモリーコントローラーの省電力モード入り)を禁止してアクセスを強制的に行なわせることで、無駄なCPUのメモリーアクセス待ちを防止することで、結果としてメモリーアクセス待ちによる無駄な消費電力を削減する。

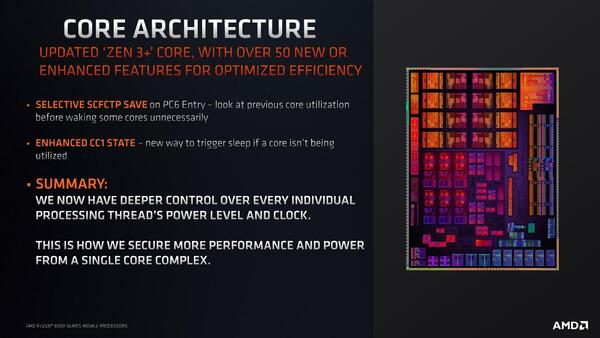

Selective SCFCTP Save

(不要なコアの無駄な起動の防止)

SCFCTPが何の略なのかは実は不明なのだが、AMDが2013年に出願、2018年に取得した特許の中で、SCFCTPというデータブロックが3次キャッシュ中に置かれることが記述されている。

このSCFCTPというのはバスの調停機構(Zen 3/3+の場合はインフィニティー・ファブリック)に関係するもので、イベントが発生した際に、CPUはSCFCTPブロックを参照してCPUをC0に復帰させる。ただ、例えば8個のコアのうち、待機状態に入る直前までの間活発に動いていたコアが2個だけだったとすると、8個のコアを全部一斉に復帰させる必要性は薄く、直前まで動いていた2コアのみで良いと考えられる。

そこでSCFCTPはこの2コア分のみ保存し、残りの6コアはSCFCTPに保存しないことで、不必要に復帰時の消費電力を引き上げない仕組みと思われる。

Enhanced CC1 State(C1ステートをより多様化)

コアが稼働している/していないは、従来はCPUのパイプラインの動作状況で判断していたが、新たに他の稼働している/いないの指標を追加して、積極的にコアをC1(軽い待機状態)に持ち込む工夫が追加された。

性能を直接的に引き上げる変化は残念ながら一切ないが、より性能/消費電力比を引き上げる工夫はふんだんに盛り込まれている。これらのすべてかどうかは断言できないが、少なからぬ工夫はZen 4にもおそらく盛り込まれることになると思われる(例外はLow Leakageで、Zen 4ではTSMC N5なので、また違った工夫が必要になるだろう)。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ