ロードマップでわかる!当世プロセッサー事情 第600回

CezanneはRenoirをZen 3に置き換えただけでなくあちこち再設計されている AMD CPUロードマップ

2021年02月01日 12時00分更新

ダイサイズから見るRenoirとCezanneの違い

CezanneはGPUが巨大化しメモリーコントローラーが小型化

次はRyzen 5000 Mobileシリーズについてだ。冒頭でも触れたように、Cezanneコアの特徴そのものについてはすでにKTU氏の解説があるので、氏が触れていない話をいくつか。まずはダイそのものについて。

Cezanneコアは180mm2と発表されており、156mm2のRenoirよりも一回り大型化しているのだが、せっかくダイの詳細が公開されているので比較してみた。

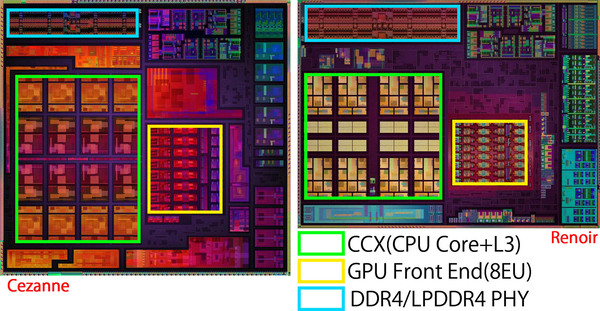

CezanneとRenoirのコアサイズ比較。Renoirのダイ写真の出典は連載555回より

左がCezanne、右がRenoirである。今回縦横比が両方で同じかどうか判断する基準がなかった関係で、Renoirが156mm2相当になるようにCezanneのサイズを縦横比一定のまま拡大しているので、ひょっとすると縦横比が多少正確ではない可能性がある。

さてそれはさておき。こうして両方を見比べてみると、実はCezanneはRenoirのCPUをZen 3に置き換えたという以上に結構あちこち再設計されているのが見て取れる。

まず黄緑色がCore+3次キャッシュの部分である。ここはそもそもZen 2→Zen 3でエリアサイズが大型化した(はず)なうえ、3次キャッシュも4MB×2→16MBと倍増している関係で、縦方向に長くなっている。実際にCCX部分(緑)の面積はRenoirが39.5mm2、Cezanneは47.7mm2ほどで、2割ほど増えている格好になる。

そこまではいいのだが、肝心のコア部の面積は? というと、Renoirが2.22mm2、Cezanneが2.20mm2と、むしろZen 3の方がエリアサイズが小さくなっているいう、やや辻褄が合わない話になっている。

あいにくZen 3(つまりVermeer)はまだダイ写真を公開していない関係で答え合わせができないのだが、もしかしたらZen 3のCPUコア部のエリアサイズはZen 2より小さくなっているのかもしれない。

逆に、同じ8CUのVegaコアにもかかわらず、明らかに大型化しているのがGPU部である。黄色がフロントエンド部(つまりシェーダー部)であるが、Renoirがおよそ11.2mm2、対するCezanneは15.1mm2ほどで、明らか内部配置などが異なっているし、CUの間隔ももう少し縦方向にゆとりがある。

そもそもRenoir→Cezanneでは350MHzほど最大動作周波数が引きあがり、その一方で消費電力は同等になっているわけだが、ここまで寸法が異なるというのは、同じ消費電力でもより高速動作が可能なように、物理的に作り直された可能性が大である。

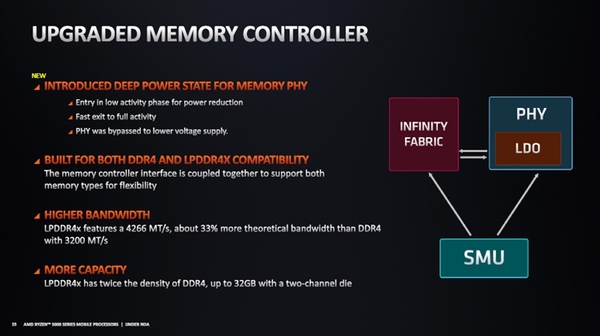

その一方で、より省電力動作が可能になったというメモリーコントローラーの物理層(水色)に関しては、Renoirが14.7mm2ほどなのに対してCezanneは8.7mm2ほどと大幅に小型化されている。また枠では囲わなかったが、メモリーコントローラー物理層の右にあるブロック(おそらくUSBのコントローラーやPHYと思われる)も微妙に小型化しているなど、ほぼすべてのブロックに手が入っていることがわかる。

Cezanneで強化されたメモリーコントローラーの概要。メモリーの物理層(PHY)に手が入っており、省電力状態(Deep Power State)から素早くフルパワー動作へ、またはその逆へ遷移するようになる

LucienneはRenoir Refreshではなかった

ついでにLucienne(ルシエンヌ)について。KTU氏も深くは突っ込んでいないのだが、AMDの担当者に確認した限りで言えば、Lucienne≠Renoir Refreshということが確認できた。つまりLucienneはRenoirがベースではなくCezanneがベースとなっており、ただしCPUがZen 2というやや不思議な構成になっている。

実際LucienneとRenoirを比較すると、CPUに関してはほぼ同じ程度の動作周波数で3次キャッシュの容量もRenoirと同じだが、新たにCPPC2での電力制御がCezanne同様に行なわれている。

一方、GPUに関しては明らかにLucienneの方が高い動作周波数で、しかもCU数が多い。CU数に関して言えばTiger Lakeとの比較の中で少しGPU性能を引き上げたというあたりだろうが、動作周波数についてはRenoirベースのままでヘタに上げるとTDP枠をはみ出すから、そうそう上げられない。このあたりはCezanneのGPUコアを利用することで、GPU性能の引き上げが可能になったわけだ。

ただ正直言って、わざわざZen 2コアベースの派生型を混ぜるべき理由がさっぱりわからない。それもRenoir Refreshであればまだしも、そうではないとなるとAMDの意図が理解できない。とりあえず連載597回で書いた、「LucienneとはRenoir Refresh」というのは間違いであったことを報告しておきたい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ