データ処理中心のアーキテクチャーにするため

CPUをバラバラに分解して再配置した「TSP」

久々のAIプロセッサー連載となる。今週はGroqという会社のTSP(Tensor Streaming Processor)というチップを取り上げたい。Groqは2016年創業の会社。創業者はJonathan Ross氏(当初はCTO、2018年末からCEO)とDoug Wightman氏(2018年末までCEO)、それとChamath Palihapitiya氏(現在も会長を務める)といったメンバー。いずれもGoogleの出身である。

特に現CEOのRoss氏は、GoogleでTPU(Tensor processing unit)の開発をしていた人間である。Wightman氏はGoogle Xの“moonshot factory”のエンジニアだった。創業メンバーには、他にXilinxで18年務めた後でGroqにCOOとして参加したKrishna Rangasayee氏などもいたが、氏は2018年11月に辞任、SIMa.aiという別のAI向けプロセッサー企業を創業するなどしている。

この2018年末というのは、会社の方針を巡っていろいろ内紛とまではいかないもののゴタゴタがあったらしいのだが、そのあたりはあまり外には伝わってきていない。ただこうしたことがあると、最終的に製品が出ないままに空中分解なんてこともベンチャー企業では珍しくない。

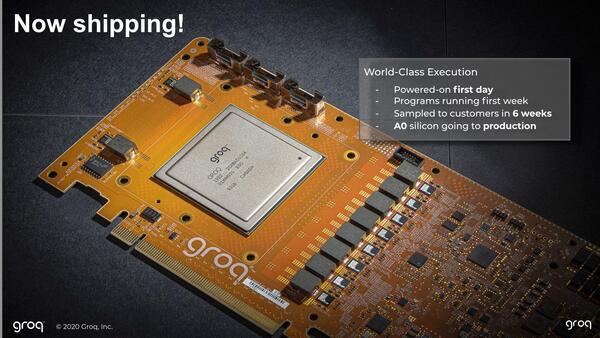

実際、昨年のAI Hardware Summitにおいて同社はスポンサーをしていたにも関わらず出展を取りやめており、会社そのものの存続が危ぶまれていたのだが、幸いにも同社はそうした危機を無事乗り越え、今年にはついにA0シリコンの出荷開始にこぎつけている。ちなみにAI Hardware Summit出展キャンセルの理由について、同社は「顧客の都合(Customer Issues)」と説明していた。

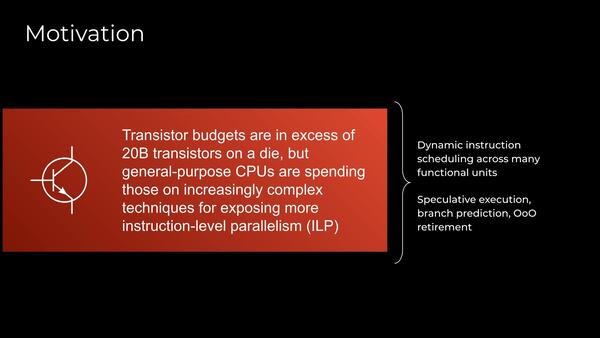

そのTSP開発におけるアーキテクチャーの根底をなす考え方が下の画像だ。

200億のトランジスタがあっても、ILPを引き上げるために複雑な仕組みを取り入れていることで利用効率が低い、というのは連載581回でスライドを掲載したPOWER 10チップを考えれば理解できる。

180億トランジスタも費やしながら、コアそのものはSMT8のものがたったの15個、最大でも120スレッドである。つまり1スレッドあたり1.5億トランジスタを使っている、という計算もできるわけで、この不効率性をなんとかしたいというのが最初のモチベーションである。

そしてAI市場の場合、それが学習にしても推論にしても問題になるのは計算密度(単位あたりのダイサイズでどれだけ計算ができるか)になる。実際x86でもArmでも、IPCなどはAIの性能にあまり寄与していない。

むしろSIMD的にどれだけ大量に計算処理を廻せるかに特化した方が効率よく動くし、そもそもAIでは条件分岐などが非常に少ない(ないわけではないが、アルゴリズム的に条件分岐を使わずにインプリメントできるケースが大半)から、そもそも従来型の命令処理中心のアーキテクチャーではなく、データ処理中心のアーキテクチャーにすることが求められている、という割り切りである。

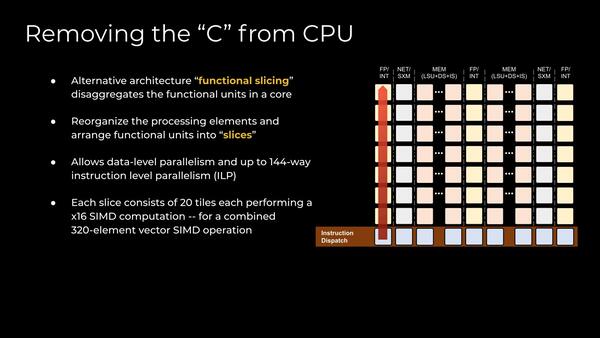

その割り切った結果が下の画像だ。考え方としてはVILWにやや似ている気もするが、もっと強烈だ。要するにOut-of-Order型プロセッサーのバックエンドにあたる部分をバラバラに分解して、それぞれを独立した“Tile”として並べる格好になる。

“CPU”(Central Processing Unit)が、ただの“Processing Unit”になるわけだ。ちなみにこの図では縦方向に7つしかTileが並んでないが、実際はこれが20個並ぶ格好だ

その意味ではDSPというか、多分一番近いのはXilinxがVersal ACAPという新しいFPGAで投入するAI Coreと呼ばれる独自アクセラレーターコアだと思うが、そんな説明ではわからないだろう。

上の画像は概念であるが、例えばFP/INT演算ならそれだけを実行するコア(Groqの用語で言えばTile)を20個並べて(これは縦方向)、Sliceと称する。処理はこのSliceの単位で行なう形になる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ