(3) Ring Bus

共有バスとPoint-to-Pointの折衷案のような構造が、このRing Busである。

| Ring Busの仕組み | ||||||

|---|---|---|---|---|---|---|

| メリット | 1本の共有バスでありながら、同時に複数のデバイスから送信可能。 デバイスの数を増やすのも容易。 |

|||||

| デメリット | デバイスの数を増やすと、それにあわせてレイテンシーもどんどん増えていく。 複数Ringを組み合わせるとさらにレイテンシーが増える。 |

|||||

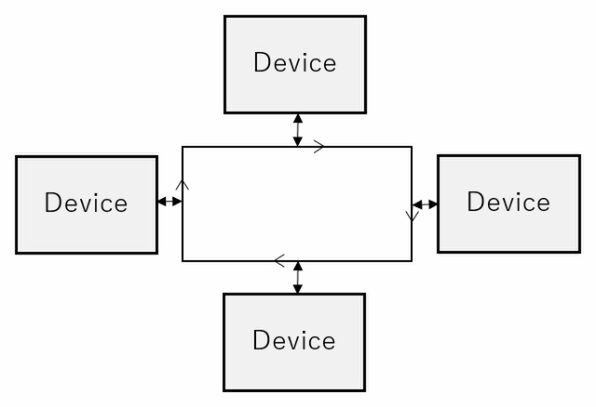

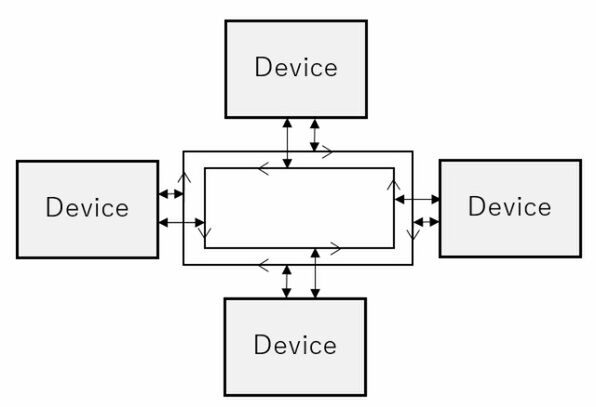

ちなみに基本は上図のSingle Ringであるが、これだと隣り合ったデバイス同士でも方向によっては1周することになってしまうので、下図のように向きを変えた二重Ring方式を取るケースが非常に多い。

このRing Bus、古いところではIBMが開発したToken RingというNetworkの一種(IEEE 802.5として標準化されている)がこの形式であり、なにげにCPUでも広く使われている。

一番愛好しているのが言うまでもなくインテルで、Sandy Bridge以降のすべてのCPUで、CPUコア同士の接続にこのRing Busを使っているほか、古くはIBM/SCE/東芝の共同開発のCell Broadband Engineが、内部のPPE(PowerPC Processor Element)とSPE(Synergistic Processor Element)の接続にRing Busを採用している。

またCPU以外でも、AMD(というか、旧ATI)のR600(Radeon HD 2000シリーズ) GPUでも内部接続にRing Busを採用していた。また、コンピューター外に目を向ければ、JR東日本の山手線やJR西日本の大阪環状線などもこの二重のRing Busだし、他にも高速道路などでも採用例は多い。

インテル以外はあまり採用例がない

では素晴らしい方法なのか?というとこれは微妙である。そもそもインテル以外のメーカーは、現在ではほとんどRing Busを使っていない。たとえばAMDはZenでInfinity FabricをSoC内の接続に採用しているが、これは名前の通りFabric、つまりSwitchベースである。

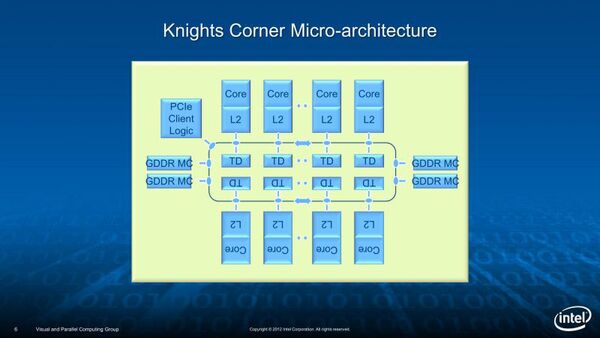

実はインテル自身もRing Busを廃した例がある。Xeon Phiの前身であるLarrabeeは、Vector Engineを追加したP5コア16個を二重Ringにつなぐ方式で、Knights Cornerもこれを引き継いだが、後継のKnights Hillではこれを2次元Meshにする予定だった。予定、というのはKnights Hillそのものがキャンセルされてしまったからだ。

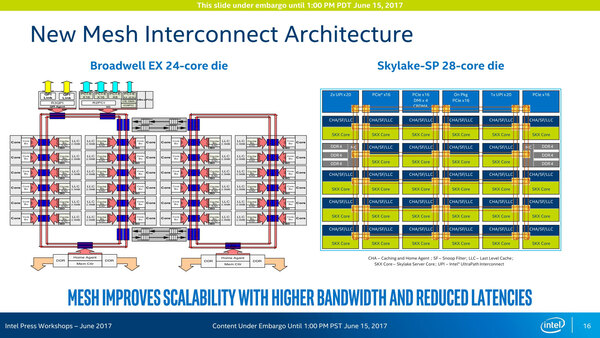

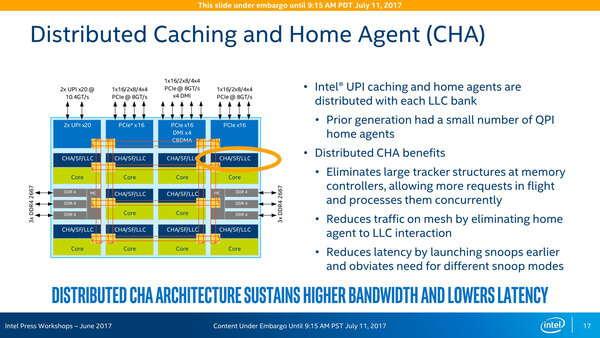

あるいはXeonについても、Broadwell世代までは下の画像左側のように2つの二重Ring BusをFIFOを介してつなぐ、というかなり無茶な構成になっていたのが、Skylake-SPから下の画像右側のように2次元Mesh構造に切り替えた。

もっとも切り替えたといってもこれはグローバルな話で、実際に詳細を見てみると、縦方向あるいは横方向同士の接続は、引き続きRing Busを使うという執念深さが見て取れる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ