Knights Cornerとの大きな違いは

単体でOSが動作すること

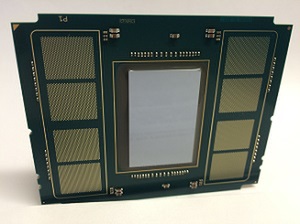

2014年11月にはKnights Landingのダイおよびパッケージ写真が公開された。

これがプレスリリースではなく、開発者向けサイトで公開されたあたりが微妙であるが、ここでさらに以下の情報が公開された。

- コア数は最大72で、コア間が2Dメッシュ構造で接続されている

- トランジスタ数は80億個以上

- AVX-512命令をサポート

大きなポイントとして、単体でOSが動作することも明らかにされている。実はこの、単体でOSが動作するという点が従来のKnights Cornerまでとの大きな違いである。

やや話が遡るが、iPSCあるいはParagonといったマシンは、いずれもすべてのノードでOSが動作していた。iPSC/2は独自のNX/2というOSが、ParagonではSNLが開発したSUNMOSという軽量カーネルのOSがすべてのノードで動作していた。

なぜこのような構造にしたかというと、たくさんあるノードを全部外部のホストから制御していたら、その制御のオーバーヘッドが馬鹿にならないためだ。

したがって、各ノードにそれぞれ軽量なOSを載せ、この上で勝手にプログラムが走るような構造にするほうがトータルとしてのオーバーヘッド削減につながる。

この問題はKnights Cornerでも顕著で、なにしろI/FがPCI Express x16レーンのみなので、ここで60コアの制御などを全部ホストからやろうとすると帯域不足が顕著だった。

ところがKnights Cornerでは個々のプロセッサーにOSが載る構造になっておらず(不可能ではないが、そもそもそれを前提とした構造ではないので非常に効率が悪い)、どうしようもないというジレンマに陥っていた。

Knights Landingではコアそのものの性能を引き上げるとともに、個々のコアで別々のOSが動作することを前提とした構造になったため、このあたりがだいぶ改善されることになった。

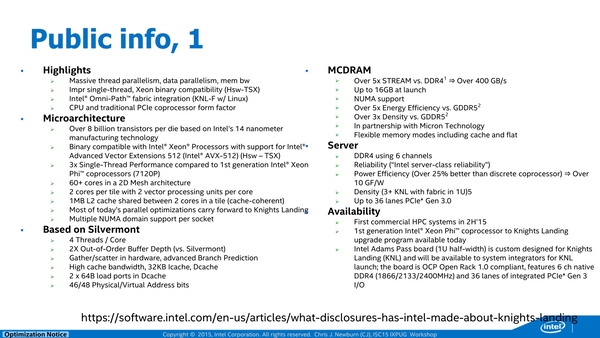

また悪名高かったリングバスを放棄して2Dメッシュを採用したのも性能改善に役立つと思われる。そして、これを利用したサーバーの構成があることも明らかにされた。このあたりをまとめたのが下の画像である。

おもしろいのはKnights Landingでは3D DRAM(左上の画像ではMCDRAM:Multi Channel DRAMと記載されている)の他に、6chのDDR4 I/Fを用意していることで、これとMCDRAMであわせて400GB(384GB DDR4+16GB MCDRAM)のローカルメモリーを利用することも可能な構成になっている。

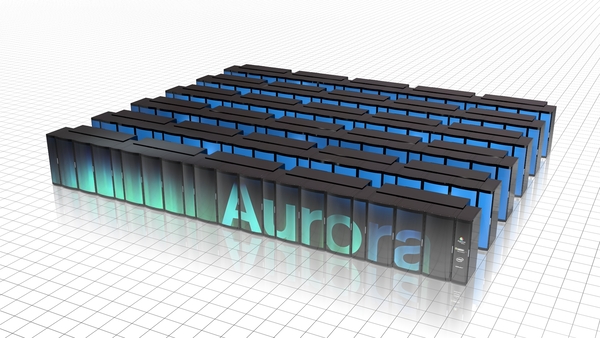

またKnights Landingを最初に利用するのはNERSC (National Energy Research Scientific Computing Center:米エネルギー省の科学技術計算施設) で、2016年中旬までに9300ノード以上を実装したシステムを構築するが、それよりも規模として大きいのはアルゴンヌ国立研究所に設置される予定のAuroraとThetaというシステムだ。

これはオークリッジ国立研究所とアルゴンヌ国立研究所、ローレンス・リバモア国立研究所の共同(Collaboration)ということで、CORALという名称がついているが、2018年までにALCF(Argonne Leadership Computing Facility)に180PFLOPSのシステム(これがAurora)と、2016年中に8.5PFLOPSながら消費電力が1.7MW(これがTheta)を納入する予定になっており、これにKnights Landingが利用される予定となっている(関連リンク)。

→次のページヘ続く (インテルに欠けている要素はなにか?)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ