バンクを増やして高速化する

DDR-SDRAMの仕組み

SDRAMは当初、動作速度が50MHz(20ns)から66MHz(15.15ns)程度の製品から始まった。しかし高速化の要求は強く、すぐに100MHz(10ns)や133MHz(7.5ns)、166MHz(6.67ns)となり、ついには200MHz(5ns)に達する。EDO DRAMの世代に比べると、若干は製造プロセスの微細化なども進んだが、CPUなどのロジック回路と異なり、プロセス微細化と動作速度の高速化は必ずしも連動していない。

高速化に当たって問題になるのは、データを保存するDRAMセルが「トランジスター+コンデンサー」で構成されていることである。最終的にはこのコンデンサーの性能を上げないと速度が上がらないのだが、これは微細化とはあまり関係がない。むしろ微細化によってコンデンサーの容量が減ると、すぐに電荷が揮発してしまったり、トランジスター自身の持つ抵抗とコンデンサーの組み合わせが高速化の妨げになることなどにより、性能が悪化しかねない状況にあった。

こうした事情もあり、DRAMセルの速度は200MHzあたりをひとつの上限として、別の方法で高速化を図ろうという方向性が模索された。それが「DDR-SDRAM」である。

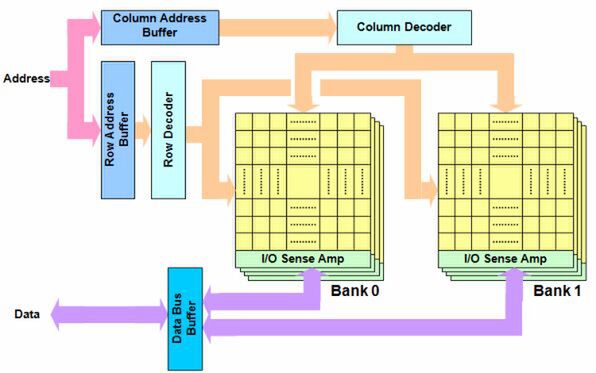

DDR-SDRAMはご存じのとおり、クロック信号の立ち上がりと立ち下がりの、両方のタイミングでデータを送信することで、2倍の転送レートを実現する技術である。これを実現するために、メモリー内部はDRAMセルのバンクを2つにしている(図3※1)。

※1 図3は説明のために簡易化したもので、実際のメモリーチップの構造はより複雑だ。もともとSDRAMは内部が4つのバンクに分割されていて、DDR-SDRAMもバンクの数は等しい。そのバンクの中が、例えば512Mbit SDRAMなら「8192×4096×4」という構成なのに対して、512Mbit DDR-SDRAMでは「8192×2048×8」になっている。この「×8」が、実際は2セルずつ同時にアクセスする形で使われる。これを「Prefetch-2」と呼ぶ。

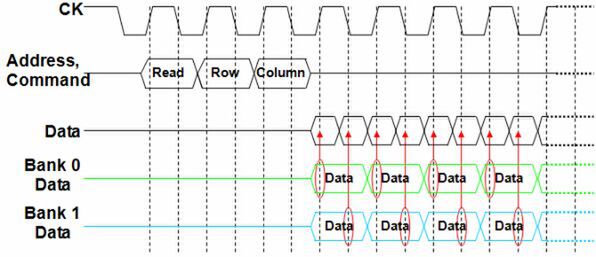

では実際の転送はどうなるのかというのが、図4である。DDR-SDRAMの場合も、最初のコマンド(図のRead)やRow/Columnの転送は、SDRAMと基本的に同じ。異なるのはその先である。

Row/Columnが渡されたら、それぞれのRow/Column Decoderが対応するセルを決定する。この際にBank 0とBank 1の両方にRow/Columnの情報が渡されるので、Bank 0とBank 1の両方から同時にデータがData Bus Bufferへと出てくる。図4の「Bank 0 Data」と「Bank 1 Data」がそれだ。

取り出されたデータは一旦Data Bus Bufferに入るが、このData Bus Bufferが倍速動作しているので、クロックの立ち上がりでBank 0のデータを、立ち下がりでBank 1のデータをそれぞれ出力する。結果として、本来の2倍のスピードでデータが送り出されるという仕組みだ。

こうした工夫により、DDR-SDRAMではDRAMセルそのものを高速化せずに、転送速度を倍増させた。ただし、転送速度を倍にするというのは信号の速度も倍になるということで、確実に信号伝達を行なうために信号電圧(=メモリーの動作電圧)を、SDRAMの3.3VからDDR-SDRAMでは2.5Vへと下げている。また、新たにDQS(Data Strobe)という信号を追加して、高速化したデータ信号の安定性を確保している。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ