これは別の観点からも説明できる。前回説明したとおり、キャッシュをアクセスするためには「それがキャッシュのどこにあるか」を毎回確認する必要がある。そのためにタグRAMにアクセスするわけだが、キャッシュの容量が大きくなると、タグへのアクセスに当然余分に時間が掛かることになる。

もちろん「セットアソシエイティブ」を使うことで、ある程度時間の増加を抑えることはできるが、Penrynコア(Core 2 Duo)の2次キャッシュのように「24ウェイ」もの構成になると、どうやっても所要時間はそれなりにかからざるをえない。そうなるとキャッシュアクセスのレイテンシーが悪化することになり、これはそのままCPU性能の足かせになりかねない。

こうしたこともあり、キャッシュも多段階構成にすることがリーズナブルであると判断された。つまり、本当に最小のレイテンシーでアクセスできるものを1次(Level 1)キャッシュとして小容量に留める。もう少しレイテンシーは大きくなるが、やや大容量のものを2次(Level 2)キャッシュ。さらにレイテンシーが大きくなるが、もっと大容量のものを3次(Level 3)キャッシュとして、それぞれ実装するというものだ。

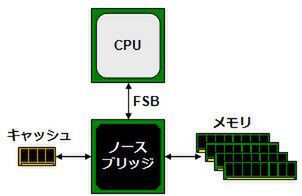

「Katmai」(初代Pentium III)やK7/K75コアAthlonの頃までは、物理的に大容量のキャッシュはCPUダイに搭載できないという問題があった(ダイサイズが大きくなりすぎ、原価が高くなり歩留まりも一気に悪化する)。そのため、まずPentiumの時代までは、図6のように2次キャッシュをノースブリッジ側に置き、キャッシュ制御そのものもノースブリッジが行なっていた。

図6 Pentium時代までの2次キャッシュの実装例

この時代のキャッシュとしては、「PBSRAM」(Pipeline Burst SRAM)が利用されていた。速度はFSBと同じ程度で、CPU内部のキャッシュに比べると数倍遅いが、最大2MB程度のSRAMモジュールが利用できた。メモリーと比べた場合、ピーク性能では大差ないが、SRAMのために理論上1クロックでアクセスできるため、レイテンシー短縮の観点でメモリーを使うよりも高速だった。

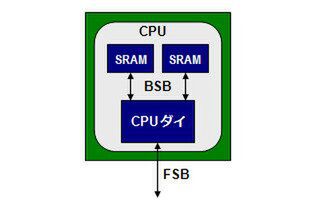

ただし、これではFSBの速度で2次キャッシュの速度が決まってしまう。そこで高速化のため、図7のようにCPUパッケージの内部にSRAM(PBSRAM)を搭載する形に進化した。ここではCPUダイとSRAMはBSB(Back Side Bus)というキャッシュ専用バスで接続され、キャッシュの制御もCPU側に移っている。

図7 Pentium Proの2次キャッシュの実装例

最初にこれを実装したのはPentium Proだが、「MCM」(Multi-Chip Module)という形で実装したところ、当時の技術では実装コストが非常に高くなりすぎてしまった。そのためPentium II/IIIやAthlonでは、大きなモジュール基板の上にCPUのダイと汎用のPBSRAMチップを載せる形で、低価格化を図っている。

ちなみにPentium Proでは、2次キャッシュの速度はCPUコアと一緒であったが、Pentium II/IIIではCPUの速度が高速化しすぎて汎用のPBSRAMチップでは追いつかなくなったため、CPUの速度の何分の1で動作する形に切り替わった。当初は「2分の1」だったが、K75では「5分の2」や「3分の1」など、いろいろ工夫をこらして何とか追いついていたものだ。

この連載の記事

-

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ -

第849回

PC

d-MatrixのAIプロセッサーCorsairはNVIDIA GB200に匹敵する性能を600Wの消費電力で実現 - この連載の一覧へ