MCMでのデュアルコア化でイージーにCPUを増やす

Pentium Pro世代での2~4CPU構成は、サーバー用途には広く利用されたが、ことデスクトップ向けにはなかなか普及しなかった。これは一重にインテルの価格政策によるものである。インテルはこうした2~4CPU構成を可能とするCPUやチップセットには、通常のデスクトップ/ノート向けよりもはるかに高い値段付けをした。ゆえに、サーバーなどの場合は性能が必要だから許容されたが、デスクトップ向けではほとんど利用されなかった。

ただし、市場は関心がなかったわけではない。例えば当時、Socket 370を2つ搭載し、ちょっとばかり細工をした「Celeron」をデュアル動作させられた「ABit BP6」が、自作市場で人気を博したことからも想像できる。

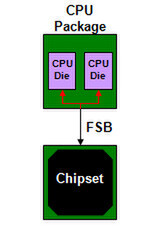

この方針をインテルが緩めざるをえなかったのは、「Pentium 4」の世代である。処理性能でAMDの「Athlon 64」に追いつかず、さらにデュアルコアの「Athlon 64 X2」の登場が目前に迫っていたこともあり、「論理的には2CPUだが、物理的には1CPU」という構成をひねり出した。これがMCM(Multi Chip Module)を使った、図3のような構成である。

この方式には以下のような利点があった。

- ●性能を引き上げながら、消費電力を低く抑えることが可能になった。

CPUの場合、ある程度以上の動作周波数で動かすためには、CPUへのコア電圧を引き上げる必要がある。消費電力はこのコア電圧の2乗に比例して増えるため、急速に消費電力が増える傾向があった。

逆に、少し動作周波数を下げるだけで大幅に消費電力が減るため、ダイを倍に増やしても消費電力は、ダイひとつの場合とほぼ同等に保つことが可能になる。

しかもダイの数が増えたことで、ダイ1個あたりの性能が若干落ちてもトータルの性能は大幅に向上した。

- ●既存のCPUパッケージにそのまま収まるため、BIOSのアップデートなどさえ行なえば、性能が倍になるアップグレードパスが構成できる。

- ●CPUダイを1個にするか2個にするか、というのは後工程※1のみで判断できる。とりあえずCPUダイを大量に作っておき、あとは需要に応じて後工程だけで1個/2個の生産の比率を調整することが可能になる。

- ●後述する2コアのダイを作るよりも、CPU 1個あたりのダイサイズが小さくなるので、歩留まりを向上できる。また生産効率そのものも増える。

- ●既存のライセンスと矛盾しない。物理的なCPUパッケージはひとつのままなので、相変わらず「デスクトップ/モバイルは(物理的に)1CPUのみ。(物理的に)2/4 CPUはプレミア価格」という構造が維持することができる。

※1 ダイをテストして、パッケージ上に実装する工程。一方「前工程」は、シリコン上に回路を構成、切り出してCPUダイそのものを作る工程。

インテルはPentium 4をベースにした「Pentium D」に続き、Core 2 Duoをベースに同じ方式を利用した「Core 2 Quad」をリリースした。2010年に入ってからは、CPUとGPUという異なるダイの組み合わせであるが、Clarkdaleが「Core i3/i5」としてリリースされている。

なお、AMDは長らくこの方式を採用してこなかったが、2010年発表された「Opteron 6000」シリーズではMCMを使い、やはり2つのコアを搭載している。

だが、こうした方式がそろそろ限界になってきたのは、以下のような問題が生じてきたからである。

- ●ダイを3つ以上実装するのが難しい。ダイ2つですら、パッケージは20層以上の積層基板で実現されており、3つ以上になるとさらに層数が増すことになる。物理的な配置も困難。

- ●FSB方式を使う場合、ダイの数が増えるほどFSBの速度を落とさないと間に合わない(信号の電気的な波形の乱れが、ダイが増えるほど増加する)。

性能を確保するにはFSBの速度を上げなければ間に合わないが、それが実現できない。

- ●ダイ同士の通信速度がFSB経由となるため、性能を上げにくい。

- ●90nmプロセス以降では省電力性を高めることが要求されつつあるが、これを実現するのが難しい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ