NVIDIAチップセットの歴史 その2

インテル向けやGPU内蔵に進出したNVIDIAチップセット

2010年04月12日 12時00分更新

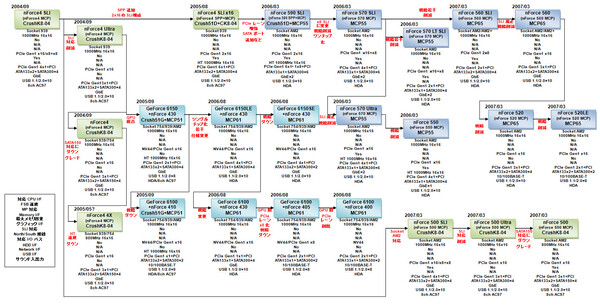

PCI Express対応のnForce4をAMD向けに投入

前回と前々回で述べたように、「nForce3」シリーズでAthlon 64/Opteron向けチップセットマーケットのかなりの部分を握ったNVIDIAの次なる製品が、2004年9月に発表された「nForce4」シリーズである。これはNVIDIAにとって初のPCI Express対応チップセットとなった。ちなみに従来同様、ワンチップ構成のチップセットとなっている。

このnForce4はまず、以下の3製品がリリースされる。対象となるのはSocket 939とSocket 754のAthlon 64/Sempronなどである。

- nForce4 SLI

- x16のPCI Express(PCIe)レーンをx8+x8と構成することで、SLI動作を可能としたモデル

- nForce4 Ultra

- nForce4 SLIからSLI機能を省略したもの

- nForce4

- nForce4 Ultraのバリュー向け。SATA 300をSATA 150にダウングレードしたり、ネットワーク用のハードウェアファイアウォール機能「ActiveArmor」などが省かれたもの

扱いとしては、nForce4 SLIがエンスージャスト向け、nForce4 Ultraがハイパフォーマンス向け(SLIは必要としない)、nForce4がメインストリーム向けという扱いである。しかし、「nForce4でもまだ高価」という評価を受けたためか、2005年の第2四半期には、「nForce4 4X」なるチップセットを非公式に投入する。スペック的にはnForce4と同一ながら、HyperTransport Linkの速度を800MHzに制限した製品である。

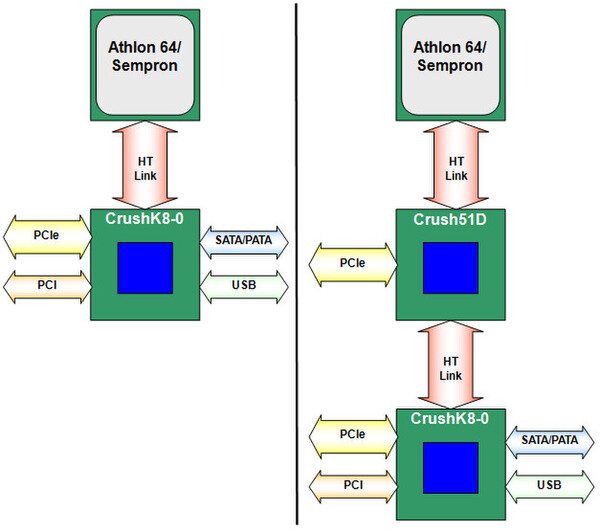

これに続き、2005年8月には「nForce4 SLI x16」をリリースする。こちらは2チップ構成となったものだが、実体はnForce4 SLIにHyperTransport PCIe Tunnelを追加した構成である。

図1の左がnForce4 SLI、右がnForce4 SLI x16の構造を簡単にまとめたものだ。要するに、右図でCPUに近い位置にある「nForce4 SPP」が追加のPCIe Gen1 x16レーンを提供することで、nForce4 MCPから出るx16レーンを組み合わせて、x16レーン構成のSLIが可能になるというものである。ちなみにnForce4 SPPは最終的に「Crush51D」というコード名になっているが、これはかつて「Crush3GIO」という名前で開発されていたものと見られている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ