|

| |

|---|---|---|

| 米AMD社 製造・テクノロジ担当バイスプレジデントのダリル・オストランダー氏 | ドイツ・ドレスデンにあるAMDの半導体製造施設“Fab 30”と最新の“Fab 36”。90nmプロセスでの半導体製品を製造するほか、65nmプロセスの量産化に向けた試作製造を行なっている |

日本エイ・エム・ディ(株)(日本AMD)は18日、東京都内にて報道関係者を集めた説明会を開催し、米AMD社 製造・テクノロジ担当バイスプレジデントのダリル・オストランダー(Daryl Ostrander)氏らにより、AMDのプロセッサー製造技術や製造プロセス技術についての説明を行なった。同社はドイツ・ドレスデンに“Fab 30/36”の2大製造工場を保有しているが、2008年までに工場の数を増やすことなく、プロセッサーの製造数量を2005年の倍である1億個に増やすとしている。

オストランダー氏のAMDでの経歴を紹介した日本AMD取締役の吉沢俊介氏によると、オストランダー氏は1981年にAMDに入社後から25年間、同社の論理回路・プロセッサーを製造する半導体工場の、ほぼすべての立ち上げに関わったという。オストランダー氏は最近の同社の半導体製造に関する話題について、90nmプロセスや300mmウエハーへの移行にスムーズに成功したほか、米IBM社との研究開発におけるパートナーシップが成功裏に推移し、現在では両社の協力関係は2011年まで延長されることとなっていると述べた。同社は現在ドレスデンにある2つの半導体ダイの製造工場に加えて、ペナン(マレーシア)、シンガポール、蘇州(中国)にも製造施設(後処理工程)を持つ。またシンガポールの半導体製造企業Chartered Semiconductor Manufacturing社(チャータード・セミコンダクター、以下Chartered)でも、AMD64アーキテクチャーのCPUの製造を行なう。オストランダー氏は今後ダイの製造工場をさらに増やすことなく、2005年から2008年までにダイの生産量を倍増し、2008年には1億個のプロセッサーを出荷するとの見通しを示した。

現在Fab 30では90nmプロセスの200mmウエハーで月産3万枚を、Fab 36では90nmプロセスの300mmウエハーで月産2万枚の製造を行なっている。特に最新のFab 36については次世代の65nmプロセスでの生産を重視していて、現在は2006年下半期の量産に向けた試作を行なっているという。2007年中には65nmプロセスに完全に移行、さらに次々世代の45nmプロセスも、2008年中に生産を開始するというスケジュールどおりに進んでいるとのことだ。

|

| |

|---|---|---|

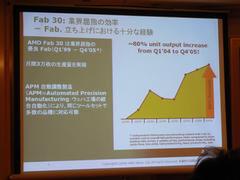

| Fab 30での製造数量変化を示すグラフ。2001年のスタート時期から80%増の増量を果たしたとする | こちらは歩留まりが一定水準に達するのに要した数量を示して、歩留まり向上がプロセス技術の改良と合わせて進んだことを表わすグラフ |

Fab 30は“業界屈指の効率”でウエハー生産を行なっているとのことで、オストランダー氏は歩留まりの向上率やプロセス世代移行の迅速さを示すグラフを提示しながら、Fab 30での生産効率の良さを説明した。その鍵となるのが“APM(Automated Precision Manufacturing:自動調整製造)”テクニック(詳細は後述)であるという。このほかにもIBMとの技術開発におけるパートナーシップは、65nmプロセス技術の製造ラインへの導入や歪みシリコンの改良、45nmプロセスの開発などで着実な成果を上げているとした。この協力関係が2011年まで延長されることにより、32nmや22nmといった今後のプロセス技術での協力も進むとされる。

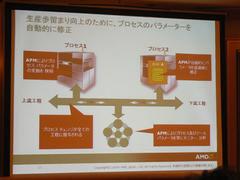

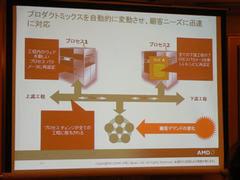

オストランダー氏の後を受けて、日本AMD 品質保証部部長の鈴木屹(すずき たかし)氏により、生産管理におけるAMDの差別化要因についての説明が行なわれた。1つは先に触れたAPMで、400件以上の特許で構成される自動化された意志決定機能であるという。APMの例としては、CPU製造のある工程でプロセスパラメーターの変動があると、APMがそれをモニターして他の工程や同じ工程の他ラインのパラメーターを最適に修正するといった処理を自動で行なえるという。また顧客ニーズの変動に合わせてパラメーターを再設定することも可能という。APM技術はAMD64の製造を委託しているCharteredの製造工場にも移植され、生産管理に応用された結果、初期歩留まりとパフォーマンスの向上を実現したとのことだ。

|

| |

|---|---|---|

| APMの例。プロセス1でのパラメーター変動をモニターが自動で検知し、それに合わせて他のプロセスのパラメーターを自動調整する | 別の例。市場の変化に合わせてウエハー製造のパラメーターを変更すると、変更に合わせた再設定がすべての行程に自動で行なわれる |

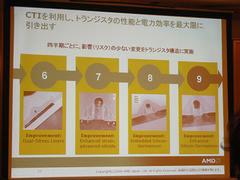

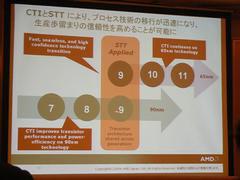

“CTI(Continuous Transistor Improvement)”と称する技術は、トランジスター製造の技術を四半期ごとに継続的に改良する。また“STT(Shared Transistor Technology)”では、プロセス世代の移行期(90nmから65nmなど)には同じトランジスター技術を異なるプロセスに適用することで、移行期に生じるリスクを軽減する。たとえば90nmプロセスで培われたトランジスター技術を、縮小してそのまま65nm世代でも使用する。歩留まりの向上した技術をそのまま次世代プロセスでの製造に利用できるため、次世代プロセスの歩留まりを向上させられるというわけだ。

|

| |

|---|---|---|

| CTIの例として提示されたスライド。歪みシリコンの導入から、徐々に歩留まり向上に適した構造に改良を行なっていく | STTの概念図。90nmプロセス世代の最後の構造を、そのまま65nmプロセスでも共有。歩留まりの高い構造をそのまま利用できる |

鈴木氏はAPMにCTI、STTを連携させることで最新技術を生産ラインに速やかに移行できるほか、顧客の要望にも迅速に対応できるとした。成功例として挙げられた事例では、ある顧客が同社に1四半期で70万個の注文を出し、100万個に上昇する可能性も伝えられていたところ、実際には注文はさらに増大。しかし同社はそれに対応できて、最終的には1四半期で120万個の納品に成功したという。これらの生産管理技術の向上によって、工場の数が少ない同社でも、多くの製造工場を要するライバルである米インテル社に対抗できているとのことであった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります