GAAからCFETへ、配線革命の「現在地」と「課題」

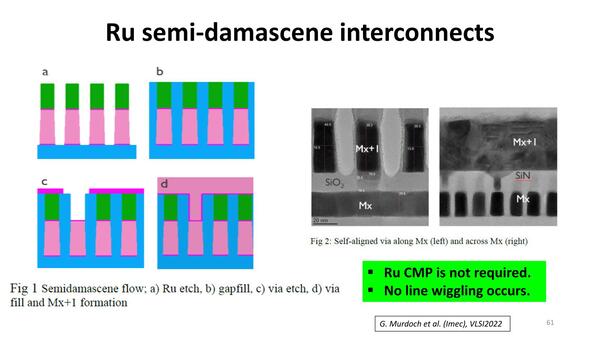

次は層間配線である。セミ・ダマシンを利用することで、Ruを利用した層間配線の構築そのものは容易であるとされている。

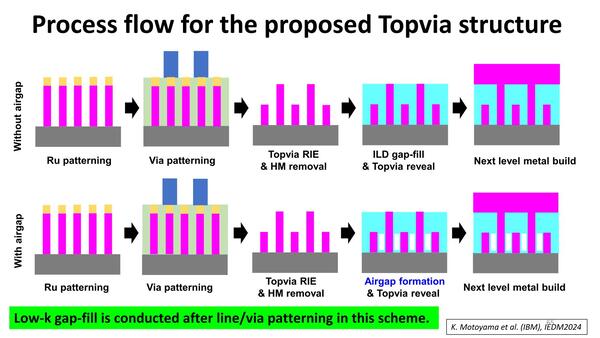

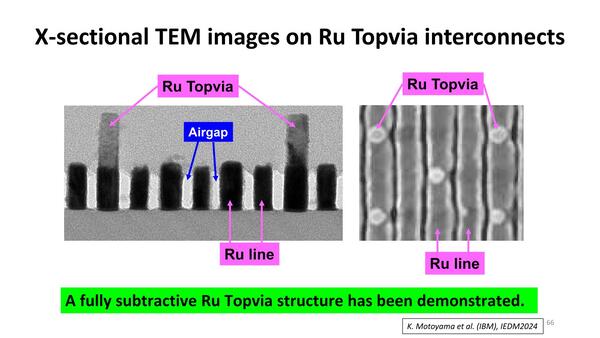

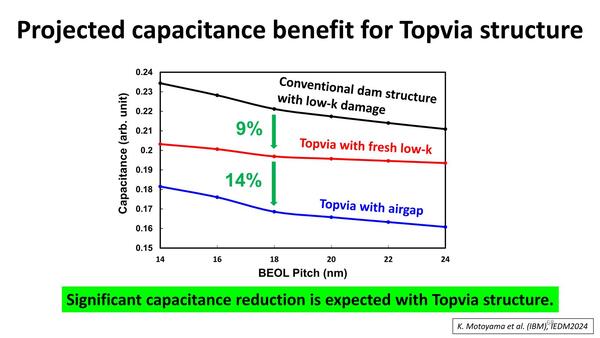

層間配線に関してもいろいろ提案されており、例えばTopviaを構築する方法ですでに構築した例も示されている。

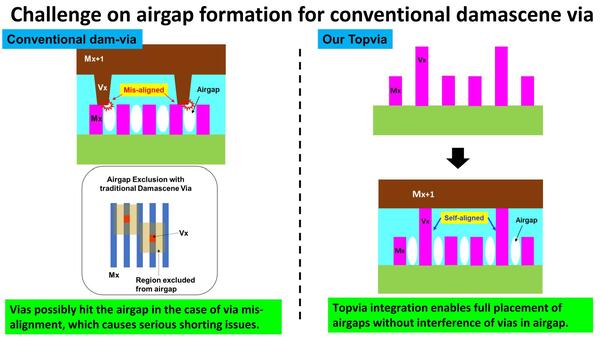

この構造が従来と異なるのは、上の層を構築する際にAirgapを破壊する心配がない点にある、とされている。

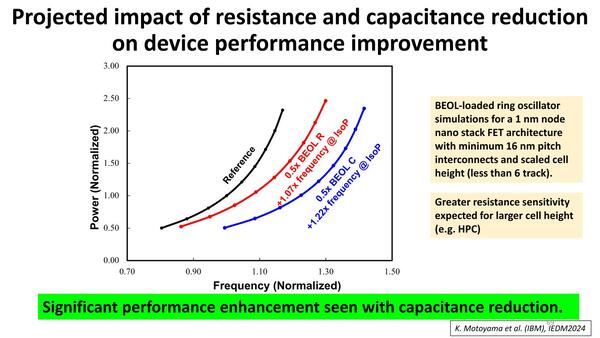

配線間の容量は、従来の製法からAirgapにすることで23%の削減となり、動作周波数という観点で言えばより少ない消費電力で1.22倍の高速性能を実現できるとされている。

より少ない消費電力で1.22倍の高速性能を実現。配線が動作周波数におよぼす影響の大きさがわかるという話でもある。トランジスタは1nmのナノスタックFETを利用してRing Oscillatorを構築したケースのシミュレーションデータだそうだ

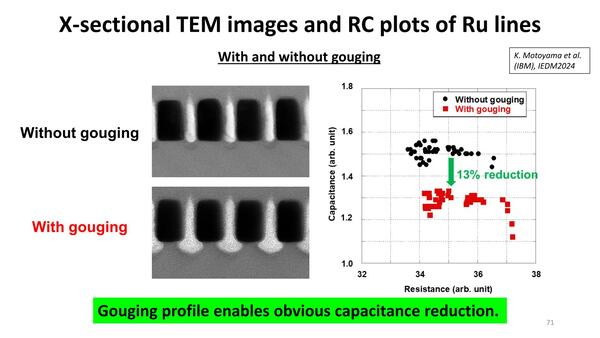

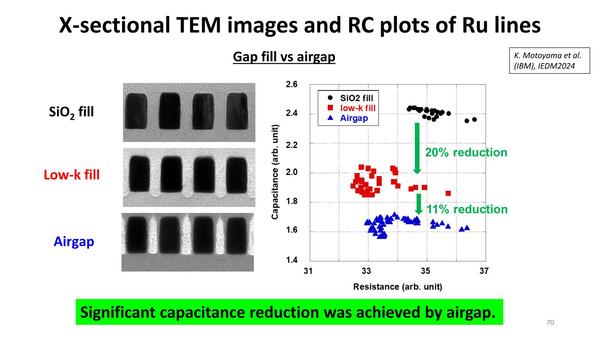

抵抗値と容量の違いを見たのが下の画像であり、ラフに言えば容量の削減の方が効果として大きいことが理解できる。さらにGougingという技法を使うと容量を減らせることも確認されている。

抵抗値と容量の違い。横軸は抵抗、縦軸が容量となる。一番抵抗が少ないのはLow-k Fillで、Airgapならわずかに抵抗は増えるが、それでも容量が大きく減るのでトータルではAirgapが一番効果的となる

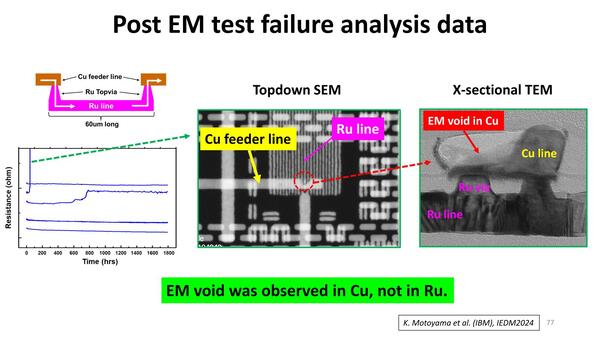

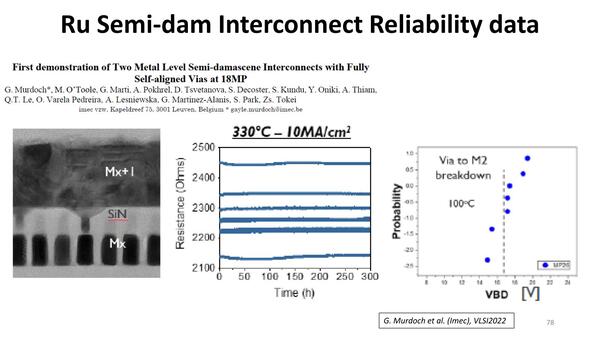

長期信頼性としては、Ruで構築した配線層の上に銅配線層を重ねて長時間稼働をさせたところ、銅配線の方にエレクトロマイグレーションに起因する空所が発生した(つまりRu配線の方は問題なし)としており、高温環境下での耐久試験でもそれなりの信頼性が確保できていることが示されている。

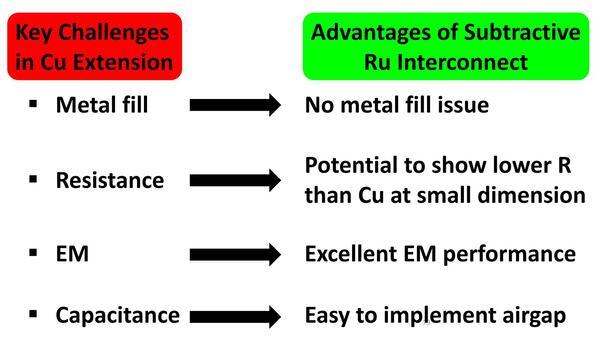

最後に結論として、現在の銅配線で問題になっているさまざまな問題はRuに切り替えることで克服可能であることを示している。

とはいえ先に説明したように、TiNなどを広範に使う必要があり、アスペクト比を高めようとすると高コストになるというあたり、まだ課題がある。現在のRibbon FET世代はもちろんのこと、次のCFETの世代でも間に合うかどうか、という感じかと思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ